Introduction

Welcome to the home page of the integrated chip project: "A 4th-Order Continuous-Time Analog Filter Designed using Standard Cells and Automatic Digital Logic Design Tools". This chip is a continuous-time analog 4th-order low-pass Butterworth filter with digitally controlled trimmable cut-off frequency. The entire design was exclusively specified in Verilog HDL code using standard cells. The physical design was exclusively accomplished using automatic digital logic design tools. The project demonstrates a method to dramatically speed-up analog integrated circuit design by applying digital integrated circuit design techiques.

This project was developed and executed under the supervision of Prof. Kinget as part of the Spring 2015 course, "VLSI Design Lab (E6950)".

The die silicon and fabrication was funded by a generous contribution from MOSIS under the MOSIS Educational Program (MEP).

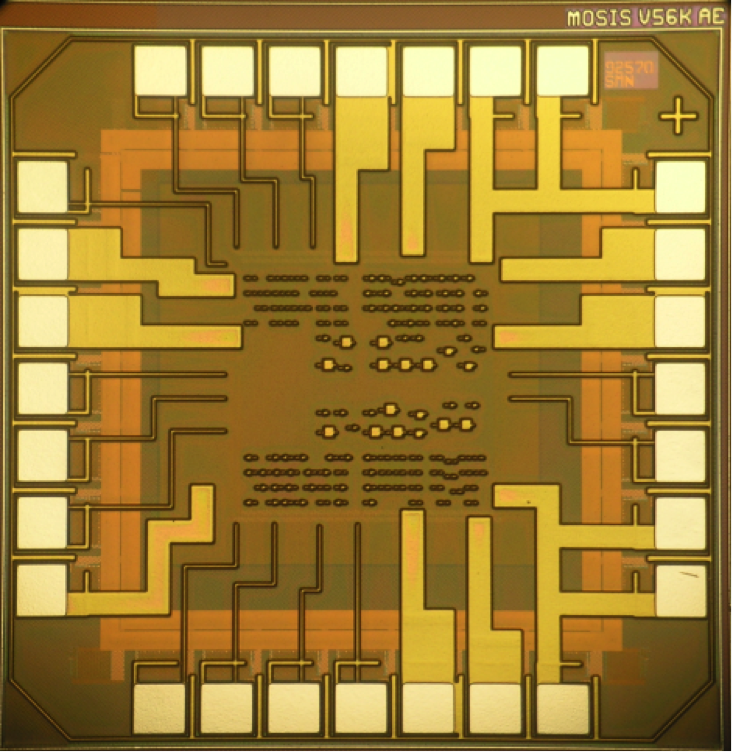

Die Photo