Block Design

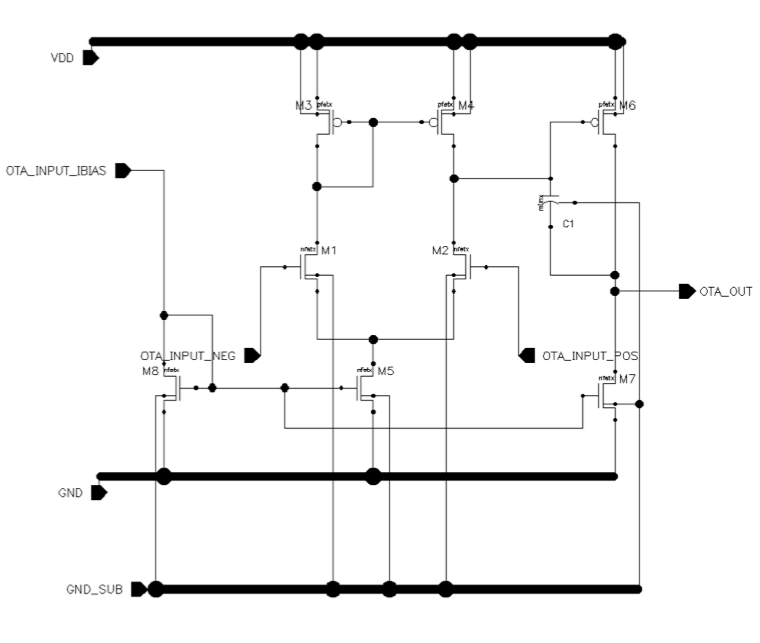

OTA

Here, we adopted a two-stage Miller OTA, as shown in Fig. 1. The OTA has a simulated DC gain of 70 dB and phase margin larger than 60 degree. It uses an 20 uA biasing current with a power dissipation less than 300 uW.

Fig. 1: Transistor-level design of OTA

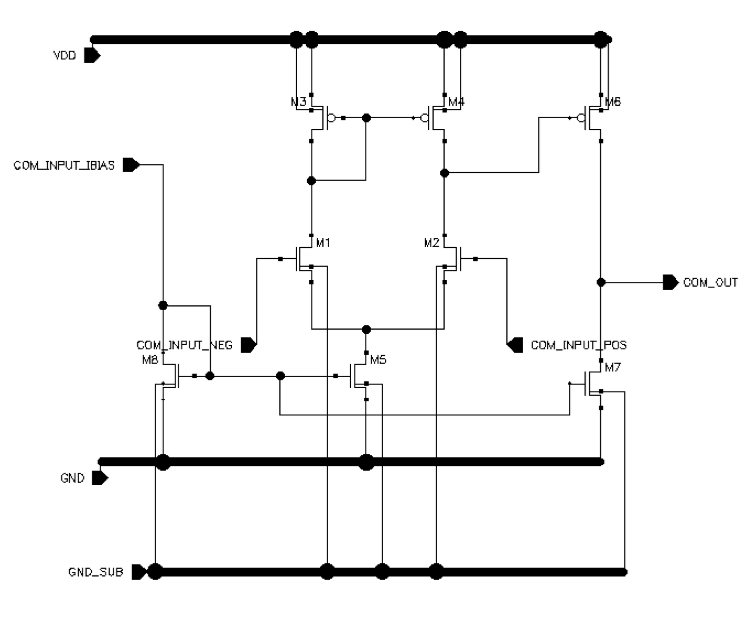

Comparator

We used a two-stage differential-input single-ended output OpAmp for our comparator, as shown in Fig. 2.

Fig. 2: Transistor-level design of Comparator

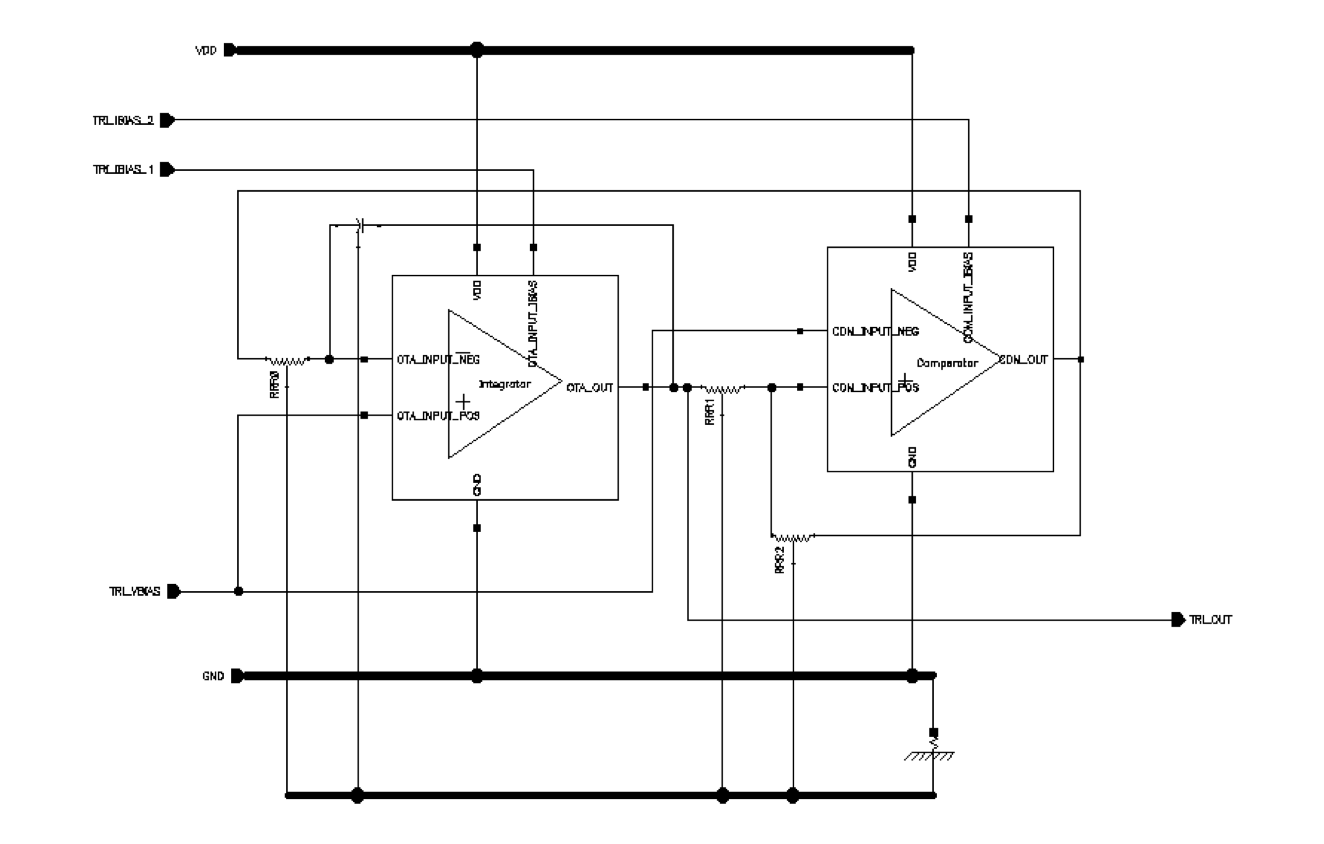

Triangle-wave generator

We adopted a triangle wave generator, using an integrator driving a comparator that is connected as a Schmitt trigger, as shown in Fig. 3. The detailed discussion is given in the literature [1].

Fig. 3: Transistor-level design of triangle wave generator

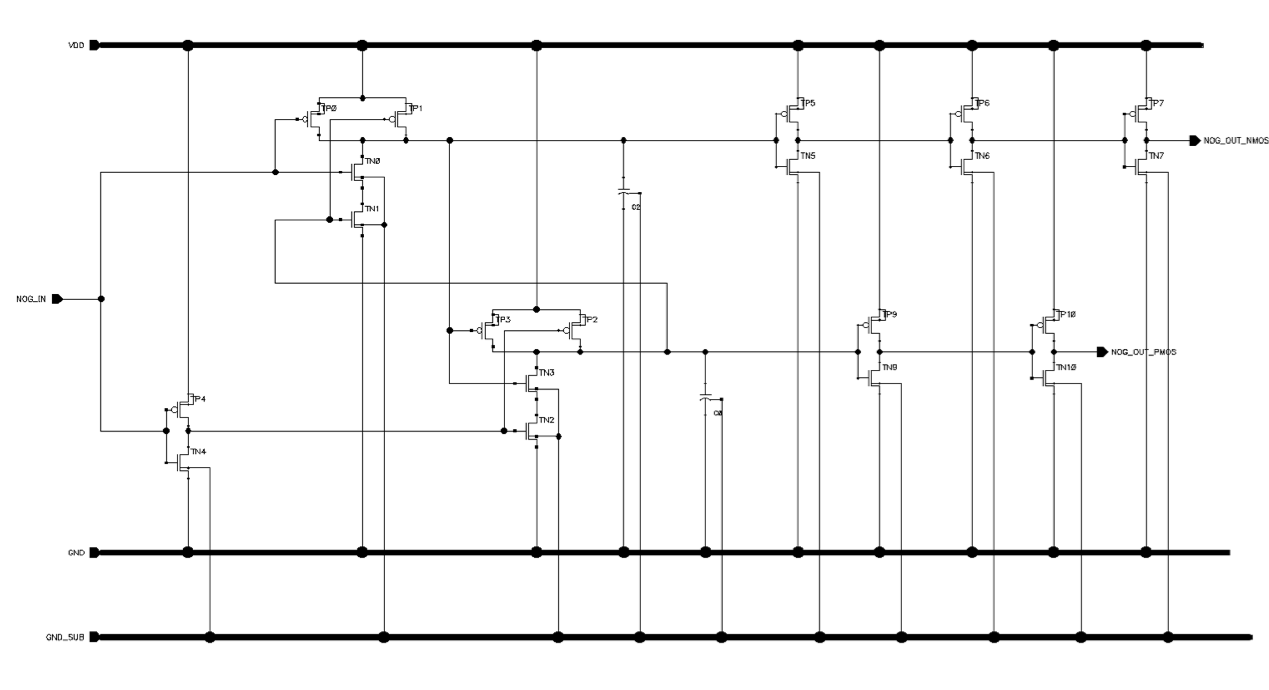

Non-overlap generator

The non-overlap generator comprises two NAND gates, one NOT gate, two capacitors and two buffer chains. The transistor level implementation is shown in Fig. 4.

Fig. 4: Transistor-level design of non-overlap generator

Output driver

The output driver is a simple inverter, composed of one NMOS and one PMOS. The primary consideration while determine the size of two transistors to achieve a high efficiency. As a rule of thumb, we should reduce the on-resistance of both transistors to let most of the voltage drop by the load resistor.