Introduction

This website documents the design, tape-out, bring-up and test of a custom IC -- a superheterodyne upconversion receiver for AM. The chip was created as part of the Spring 2023 EE6350 VLSI Design Lab offered by Professor Peter Kinget and Columbia University, and sponsored by Apple Inc. The chip was fabricated using TSMC 65nm CMOS technology.

MOTIVATION:

The motivation behind building a superheterodyne AM receiver was to gain experience in the system and circuit design of a standard receiver front-end architecture, while maintaining realistic goals that were acheivable for our first full tape-out process. The superheterodyne single conversion IF architecture is commonly used in many different digital and analog communication channels; the semi low-frequency AM radio band loosened the circuit design contraints relative to more commonly used high-frequency bands -- yielding a relevant and acheivable project goal. All circuit blocks on the chip are custom-designed, and all layout and top level integration was done by hand.

PROJECT OVERVIEW:

We The fundemental goal of the project was to build a superheterodyne upconversion IF Receiver for AM capable of detecting, processing, and demodulating AM radio channels. The IC was integrated onto a custom-designed PCB to create a portable AM radio module powered by three AA batteries.

The system block diagram is paritioned into four modular sub-sections on chip defined with respect to operating frequency:

- AM radio-frequency front end (RFFE): [540-1700] kHz

- Voltage controlled oscillator (VCO): [9-10.16] MHz

- Intermediate-frequency amplifiers (IFA): [10.7] MHz

- Audio baseband processing (BBP): [0-3] kHz

This partition allows for independent test and implementation of the respective receiver blocks during bring-up, test, and demonstration.

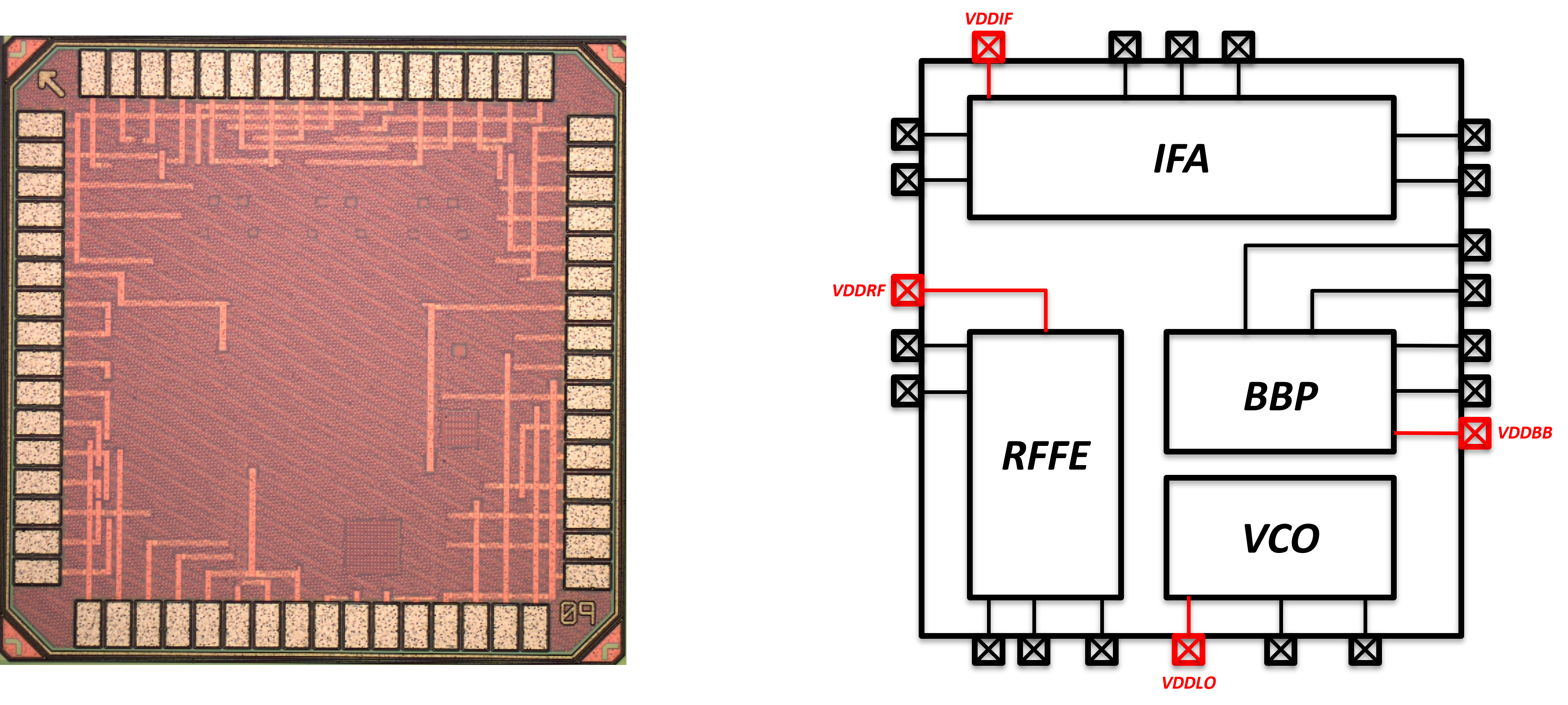

The die photo of our chip and a corresponding block diagram of our floorplan and signal path pins are shown below -- the culmination of our cumulative efforts in the Spring 2023 EE6350 VLSI Design Laboratory.