# Matching the Power, Voltage, and Size of Biological Systems: A nW-Scale, 0.023-mm<sup>3</sup> Pulsed 33-GHz Radio Transmitter Operating From a 5 kT/q-Supply Voltage

Jaebin Choi, Eyal Aklimi, Chen Shi, David Tsai, Harish Krishnaswamy, *Member, IEEE*, and Kenneth L. Shepard, *Fellow, IEEE*

Abstract—This paper explores the extent to which a solid-state transmitter can be miniaturized, while still using RF for wireless information transfer and working with power densities and operating voltages comparable to what could be harvested from a living system. A 3.1 nJ/bit pulsed millimeter-wave transmitter, 300  $\mu m$  by 300  $\mu m$  by 250  $\mu m$  in size, designed in 32-nm SOI CMOS, operates on an electric potential of 130 mV and 3.1 nW of dc power. Farfield data transmission at 33 GHz is achieved by supply-switching an LC-oscillator with a duty cycle of  $10^{-6}$ . The time interval between pulses carries information on the amount of power harvested by the radio, supporting a data rate of  $\sim 1$  bps. The inductor of the oscillator also acts as an electrically small  $(\lambda/30)$  on-chip antenna, which, combined with millimeter-wave operation, enables the extremely small form factor.

Index Terms—Antennas, low power design, monolithic integrated circuits, radio frequency oscillators.

# I. INTRODUCTION

OLID-STATE systems and biological systems have many complementary capabilities. For example, solid-state systems are uniquely capable of coupling to the radio-frequency (RF) electromagnetic spectrum for the transfer of information, while biological systems have capabilities for specific molecular recognition and the exploitation of biochemical energy sources. Nevertheless, biological systems and solid-state systems are characterized by fundamentally different physical form factors, power densities, and operating voltages, which create many challenges in mating these functions, most evident in the area of implanted medical devices [1].

In this work, we explore the extent to which solid-state systems can be miniaturized, while still using RF for wireless information transfer and while working with power densities and operating voltages comparable to what could be harvested from

Manuscript received December 26, 2014; revised April 05, 2015; accepted April 14, 2015. Date of publication July 17, 2015; date of current version July 24, 2015. This work was supported in part by the Keck Foundation and by the Office of Naval Research under Grant N00014-13-1-0375. This paper was recommended by Associate Editor P. Y. Chiang.

- J. Choi was with Columbia University, New York, NY 10027 USA. He is now with the Korea Institute of Science and Technology, Seoul, Korea (e-mail: jaebin@kist.re.kr).

- E. Aklimi, C. Shi, D. Tsai, H. Krishnaswamy, and K. L. Shepard are with Columbia University, New York, NY 10027 USA (e-mail: aklimi@ee.columbia.edu; chenshi@ee.columbia.edu; dtsai@ee.columbia.edu; harish@ee.columbia.edu; shepard@ee.columbia.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2015.2426958

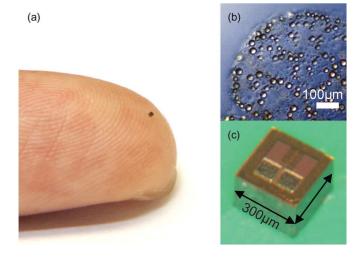

Fig. 1. (a) Transmitter on fingertip and (b) *Thiomargarita namibiensis*, at the same scale with (c) die photo.

a living system. In our case, the radio transmitter is of the scale of 300  $\mu$ m, the size of the vacuoles of large monads, such as *Thiomargarita namibiensis* (Fig. 1(b)). These vacuoles are reported to have metabolic rates on the nW scale [2], most of which support a proton motive force (PMF) across the membrane that could be harnessed to power such a system.

We explore fundamental limits to the minimum power, voltage, and size achievable for such solid-state systems. Using thermodynamic arguments, Landauer showed that there is a minimal energy required for computation at the level of  $kT \ln 2 \sim 2.85$  zJ at room temperature per bit [3]. Practical minimum energies for CMOS circuits performing active computation are achieved with subthreshold operation [4]–[6] in which leakage power is balanced against dynamic power dissipation. In our case, communications requirements demand power levels significantly above the average available power. This requires duty-cycling the solid-state system, in which long periods of inactivity are time multiplexed with substantially shorter periods of communication activity.

The lowest supply voltage at which a circuit can operate is set by the need to achieve a minimum on-current-to-off-current  $(I_{on}/I_{off})$  ratio in transistors. With digital logic involved, a supply voltage of  $\sim 4kT/q$  is needed to restore a digital state with static CMOS [7]. Since in practice, higher supply voltage levels are needed to meet other circuit requirements, such as

transistor gain for startup in analog oscillators, efficient voltage multiplication that can start-up at the available input supply voltage at the front-end is an important component in these systems.

The size of the system is limited by the need to couple to RF radiation efficiently. Small loop antennas have small radiation resistance and high reactance, making it difficult to deliver power to them. The amount of radiation produced by an ideal small loop antenna is determined by the radiation resistance  $R_{rad}=20\pi^2(C/\lambda)^4$ , where C is loop circumference and  $\lambda$  is wavelength [8]. For an ideal 300  $\mu$ m diameter loop antenna,  $R_{rad}$  is 22.8 m $\Omega$  and 0.693  $\mu\Omega$ , respectively, at 33 GHz and 2.45 GHz. The latter will inevitably be dwarfed by the ohmic resistance of the antenna, dictating higher frequencies of operation for our system.

The transmitter developed here consumes 3.1 nW in a nearly cubic 300  $\mu m$  by 300  $\mu m$  by 250  $\mu m$  form factor (Fig. 1) in 32-nm SOI CMOS. These lower power levels are achieved through extreme duty-cycling  $(10^{-6})$  of an LC millimeter-wave oscillator, in which the inductor is repurposed as an electrically small  $(\lambda/30)$  electromagnetic (EM) radiator. Power is integrated for about a second to provide the energy for an approximately 1  $\mu$ s-wide 33 GHz pulse by gating of the oscillator power supply. The large amount of capacitance required for energy storage (~14 nF on the chip) is achieved through deep-trench capacitors extending 3.6  $\mu m$  into the substrate. A switched-capacitor voltage multiplier boosts a 100-190 mV input voltage to over 300 mV to provide for oscillator startup, achieving a continuous-wave (CW) equivalent isotropically radiated power (EIRP) of more than -50 dBm and minimum reading distance of 18 cm at 10 dB SNR. The interval between pulses is inversely proportional to the energy stored, meaning that it carries information on the amount of power harvested by the radio. This information is encoded in the radio pulse stream at a bit rate of approximately 1 bps. Section II describes in more detail the trade-offs between operating power, operating voltage, and system size and the need for extreme duty cycling of the LC oscillator. The resulting duty cycling of communications puts constraints on the receiver described in Section III. Section IV describes the considerations that went into the choice of carrier frequencies. Details of the implementation of the transmitter are given in Section V with measured results in Section VI. Section VII describes how variability affects circuit performance and Section VIII concludes.

# II. TRADE-OFFS BETWEEN OPERATING POWER, OPERATING VOLTAGE, AND SYSTEM SIZE

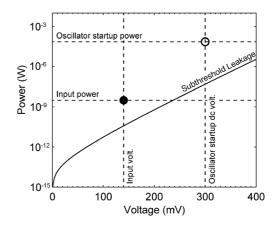

Power consumption of a logic gate consists of both dynamic and static power. The dynamic power arises from the charging and discharging of capacitance, while the static power is due to subthreshold, gate, and junction leakage. Subthreshold leakage power which dominates the other sources of leakage in the deep-subthreshold regime determines the lower bound for power dissipation in our system. Shown in Fig. 2, this power is proportional to  $V_{DD}e^{(qV_{DD}/nkT)}$ , where n is an ideality factor, typically between 1 and 1.5 [9].

In our system, the on-chip radiating LC oscillator, however, requires higher startup voltages ( $\sim$ 300 mV) than biologically available levels, which must be supplied by the on-chip voltage multiplier, and significantly higher operating power levels ( $\sim$

Fig. 2. Allowed power-voltage ranges of operation for the switched capacitor circuitry and LC oscillator are bounded by fundamental system constraints and biologically available limits. Two distinct operating points of the transmitter are marked as circles: idle (closed) and transmitting (open).

$50\,\mu\mathrm{W}$ ), both of which are noted in Fig. 2. The pair of cross-coupled devices in the oscillator must reach levels of current and voltage that ensure enough transconductance to overcome LC tank resistance and achieve startup, requiring near-saturation operation. This higher power and voltage is duty-cycled with an idle state operating at the input voltage (the power of which is also noted in Fig. 2) as described in Section III to achieve the required average power level. The system size is dominated by the on-chip single-turn inductor that also functions as an electrically small loop antenna. As the inductor becomes larger, the parallel resistance of the LC tank increases, requiring less  $g_m$  to overcome it for startup and reducing the required oscillator power consumption. Therefore, there exists a direct trade-off between system size and power consumption.

# III. COMMUNICATIONS IMPLICATIONS OF DUTY CYCLING

To meet oscillator startup dc conditions far more power-consuming than the required average power (Fig. 2), we have implemented aggressive duty cycling of the oscillator on-off control circuit. The duty cycling event can be represented as a train of rectangular functions with two core parameters: duty-cycling ratio (DC) and single pulse width  $(T_{pulse})$ .

For detection, the power received from a monotonously-on signal source  $(P_R)$  must satisfy

$$P_R + 10\log_{10}(DC) > -174 + NF + 10\log_{10}(BW)$$

(1)

where DC is the duty cycle, NF is the noise figure of the receiver in dB, and BW is the bandwidth of the transmitted pulse. BW is inversely proportional to  $T_{pulse}$ .

The duty-cycling ratio is set to approximately  $10^{-6}$  based on the ratio between the oscillator's continuous-wave dc power consumption and the available harvested power. The single pulse width that can be supported is limited by the achievable on-chip capacitive energy storage. Increased capacitive storage enables larger  $T_{pulse}$ , which reduces the bandwidth of the transmitted pulse, easing the link budget depicted in (1) at the expense of communication data rate. As we will further explain in Section V, the amount of on-chip capacitance for a chip area of 300  $\mu$ m by 300  $\mu$ m only supports pulse widths as wide as 1  $\mu$ s. With our duty-cycling ratio, this amounts to a maximum achievable data rate of approximately 1 bps.

# IV. CARRIER FREQUENCY OPTIMIZATION

To improve radiation efficiency and load matching, RFID chips to-date preferably exploit off-chip antennas which are much larger than the associated ICs, increasing overall system size to millimeter- or centimeter-scale [10], [11]. In this work, we seek to bring the size of our radio transmitter down to the hundreds-of-microns size scale. Any antenna of this size will be electrically small unless the operating frequency is scaled to THz, which is impractical in today's scaled CMOS technologies.

The use of an on-chip integrated antenna eases integration at these size scales but brings additional losses in the metallization layers and silicon substrate [12]. We use an electrically-small loop antenna that also functions as the single-turn inductive load of an on-chip LC oscillator to further conserve space. We find that a 300  $\mu$ m-diameter square loop antenna shows optimal low-power startup conditions at 33 GHz, bringing the transmitter into the millimeter-wave regime. There has been extensive recent work on highly-integrated millimeter-wave transceivers in CMOS capable of high-data-rate communication over moderate distances [13], [14]. Such transceivers commonly rely on high dc power in both the transmitter and the receiver due to the symmetric nature of the link to achieve such rates over moderate transmission distances. There has also been recent work on millimeter-wave/terahertz oscillators that operate near the  $f_{max}$ of the CMOS technology [15]. Such oscillators require the device to be biased at reasonable current densities to achieve the maximum available gain to meet stringent startup requirements.

In this application where the maximum available power is bounded by the desire to remain in the nW regime, we seek to maximize the amount of far-field radiation energy generated per unit dc power. To achieve this, we choose a carrier frequency that allows minimal power consumption while meeting the startup condition of the LC oscillator.

Transmission loss (T) is given by the following equation, where  $P_R$  is power received at the receiver antenna,  $P_T$  power inserted into the transmitter antenna,  $G_T$  and  $G_R$  antenna gains,  $\lambda$  the wavelength of the carrier frequency, and R the transmission distance:

$$T = \frac{P_R}{P_T} = G_T G_R \left(\frac{\lambda}{4\pi R}\right)^2 \times Absorp \tag{2}$$

Absorp, the amount of radiation absorbed by conductive material surrounding the antenna, is dependent on frequency. This reduction in EM field penetration depth prevents the transmitter from operating deeply in a conducting medium, such as electrolytic buffer. Skin depth ( $\delta = \sqrt{2\rho/\omega\mu_r\mu_0}$ ), the depth at which radiation power reduces by a factor of 1/e, is on the order of a few tenths of a millimeter at 33 GHz in physiologically relevant media [16]. The asymmetric nature of the link will allow the use of high-gain antennas on the receiver side to overcome high absorption for small penetration distances. In the forthcoming analysis, we assume operation under very thin tissue, hence negligible amounts of radiation absorbed.

Two main factors contribute to  $T-G_T$ , the product of radiation efficiency and antenna directivity, and the path loss,  $(\lambda/4\pi R)^2$ , as governed by the Friis transmission equation. Fig. 3(a) shows the simulated T (as determined by the product of these two factors) for the antenna assuming a receiver antenna gain of 15 dB. The increase in path loss with frequency is

Fig. 3. (a) Frequency dependence of antenna gain  $(G_T)$ , path loss  $((\lambda/4\pi R)^2)$ , and transmission loss (T); assumes 10 cm transmission distance and 15 dB  $G_R$ .  $g_m startup = 2R_{shunt}^{-1}$  is also shown. (b) Q factor and  $R_{shunt}$  of 300  $\mu$ m-wide loop antenna; simulated with IE3D assuming back-side thinning to 50  $\mu$ m.

more or less compensated by the increase in radiation efficiency of the transmitting antenna, resulting in a moderate decline with frequency.

Given that T varies by a relatively small amount of 7.8 dB across the frequency range of 1–80 GHz, the choice of carrier frequency is determined by the start-up condition of the LC oscillator which varies by 97 times (19.9 in dB) over the same range:  $g_m > 2R_{shunt}^{-1}$ , where  $R_{shunt}$  is the oscillator's shunt resistance and  $g_m$  is the transconductance of the transistors M1 and M2 (Fig. 4(g)). When on, M1 and M2 are biased in weak inversion to consume minimal current, making  $g_m$  proportional to the drain current  $I_{bias}$  [9]. Fig. 3(a) shows that the value of  $g_m$  required for startup reaches a minimum at approximately 33 GHz.

The minimum  $g_m$  startup point (Fig. 3(a)) is caused by the peaking of  $R_{shunt}$ . The loop antenna in this design can be viewed as a single-turn inductor on top of a conducting substrate. For such an inductor of a fixed dimension, there is a frequency where its Q is maximum. At low frequencies, the Q of spiral inductors is dominated by series ohmic losses in the spiral metallization and increases with frequency [17]. At high frequencies, the spiral Q is dominated by shunt substrate losses and decreases with frequency [17]. In between, an optimal frequency for Q is observed. The net shunt resistance of the LC tank,  $R_{shunt}$ , will also exhibit a resultant peak frequency. It is at this frequency that the  $g_m$  for startup is minimized. For the

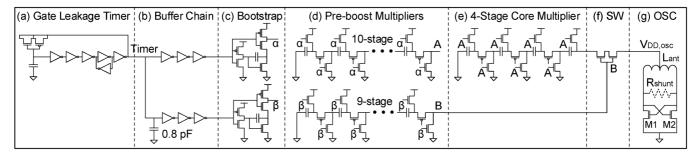

Fig. 4. System architecture.

single-turn inductor used here, this peak occurs at a frequency of approximately 33 GHz as shown in Fig. 3(b).

From Fig. 3(a), we find that at 33 GHz, startup  $I_{bias} \approx 200~\mu \rm A$  is approximately 17 times less bias current than would be required at an operating frequency of 2.45 GHz for the same form factor antenna, typical for many RFID tags, while resulting in only 4 dB less T, which can readily be overcome with improved gain on the receiver side. Our transmitter ICs are implemented with nominal oscillation frequencies  $(f_{osc})$  of 29 GHz and 33 GHz by varying the sizes of M1 and M2.

# V. IMPLEMENTATION

The transmitter system architecture is shown in Fig. 4. The entire system is controlled by an always-on  $\sim 1$  Hz timer. This relaxation oscillator uses leakage through a transistor gate of only 0.3 nA. The resulting clock controls a three-stage voltage multiplier which drives an LC oscillator, the inductor of which also acts as the system antenna. Constraints on available energy storage limit transmitted pulses to 1  $\mu$ s duration and 200  $\mu$ A current magnitude resulting in an effective duty cycle of  $10^{-6}$ .

The chip is implemented in 32-nm SOI technology that offers deep-trench capacitors with nearly 60 times higher capacitance density (250 fF/ $\mu$ m<sup>2</sup>) than metal-metal capacitors, making it an ideal energy storage device for the highly area-restricted system. These capacitors provide a total capacitance of 14 nF within the available chip area, which, if replaced with metal-metal capacitors, would occupy an area of 3 mm<sup>2</sup>. They do, however, carry a series resistance of more than 100  $\Omega$  for each 5 pF of capacitance, which must be carefully managed in the design of the voltage multiplier. Additional series resistance comes from the switches of the voltage multiplier which are operating at  $I_{on}/I_{off}$  ratios of only 40 for the first stage. The output impedances for this converter is approximately 200  $\Omega$ , creating the potential for a large transient output voltage droop. To mitigate this, three stages of voltage boosting, all with current-starved gates, are employed to provide successively better switch function at each stage, as described in Section V-B below.

We describe in more detail the design of the voltage multiplier and radiating oscillator.

# A. Ultra-Subthreshold Switched Capacitor Voltage Multiplier

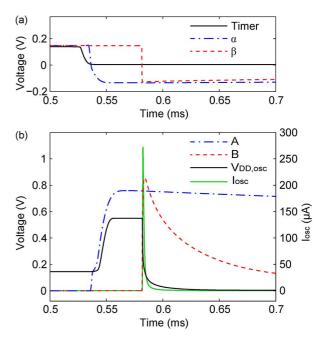

Fig. 5 shows transient behavior of critical clock signal path node voltages involved in the three stages of voltage boosting. Starting from a 130 mV swing power supply, each successive stage achieves larger swing and faster switching speed, ultimately leading to the capacitors' rapid discharge of current into the oscillator.

The entire system is controlled by an always-on  $\sim$ 1 Hz clock (Fig. 4(a)), composed of a gate-leakage unit followed by

Fig. 5. Transient simulation of critical circuit node voltages and current during a capacitor-to-oscillator charge transfer event. The antenna radiates within the narrow peak of  $I_{osc}$ . Subplots (a) and (b) display the same time window but are separated for clarity. Legend is in agreement with Fig. 4.

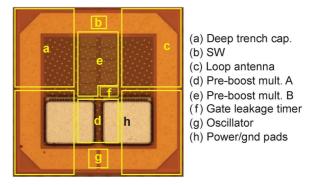

Fig. 6. Die photo with circuit positions noted.

a Schmitt trigger [18]. The 130 mV swing output of the gate leakage timer (Fig. 5(a), *Timer*) is input into two independent buffer chains, one of which is delayed by 50  $\mu$ s with the addition of a non-tunable 0.8 pF deep trench capacitor. These two time-offset 130 mV square waves emerging from these chains each feed into a bootstrapped driver, producing output swings up to 250 mV. The bootstrapped output ( $\alpha$ ) and the delayed bootstrapped output ( $\beta$ ) drive "pre-boost" voltage multipliers with ten and nine capacitors, respectively. The pre-boost output from the ten-stage multiplier (A) has a 750

Fig. 7. Gate-leakage timer oscillatory transients at  $V_{DD}$  levels given above. Current was measured by dc-powering the power/gnd pads in Fig. 6(h).

mV swing and drives the switches of the four-stage core multiplier (Fig. 4(e)), producing a more-than-300 mV supply for the oscillator ( $V_{DD,osc}$ ). The pre-boost output from the nine-stage multiplier (B), which has a 900 mV swing and is delayed approximately 50  $\mu$ s from A, opens the switch (SW) between the capacitor tank of the core multiplier and the LC oscillator, biasing the cross-coupled pair above the startup condition of  $\sim 200~\mu$ A current ( $I_{osc}$ ) for 1–3  $\mu$ s until the capacitance of the core multiplier is sufficiently discharged. The antenna radiates at 33 GHz while the oscillator startup condition is met.

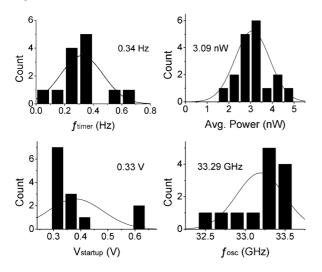

This process repeats itself at each falling edge of the gateleakage timer. The ratio of oscillator on-time to timer clock period is approximately  $10^{-6}$ . To deliver a total of 0.15 nJ, computed from LC oscillator dc power consumption multiplied by pulse duration, to the oscillator in a single pulse requires 3.09 nJ be drawn from the input supply for an overall switched-capacitor efficiency of 4.9%. Ultra-subthreshold operation of the timing circuit produced an as-designed yield of 25% for these parts as a result of random variability in 32-nm CMOS as described in more detail in Section VII.

# B. Millimeter-Wave Ultra-Low-Power Radiating Oscillator and Layout

To exploit a limited chip area of 300  $\mu$ m by 300  $\mu$ m, a single-turn loop antenna (Fig. 6(c)) acts as both the far-field radiator and the inductor of the LC oscillator. The loop is fabricated at the topmost metal layer with a path width of 40  $\mu$ m and inductance of 553 pH at 33 GHz. Similarly, millimeter-wave operation is achieved with the capacitance of the LC tank provided only by the device capacitance of the cross-coupled transistors (Fig. 4(g)). Each minimum-length (40 nm) device is given a width of 13.1  $\mu$ m. An nMOS-only oscillator is implemented as it improves the power generation efficiency of the oscillator due to the higher speed of nMOS transistors. The nMOS cross-coupled transistor pair is laid out with an arrangement suggested by Liang *et al.* that achieves maximal drain efficiency through reducing terminal parasitics [19].

The layout (Fig. 6) takes full advantage of the chip area bounded by the antenna perimeter. Deep-trench capacitors occupy much of the area under the loop inductor, providing 13.7 nF for the four-stage voltage multiplier. The center contains the metal-metal capacitors of the nine-stage pre-boost multiplier, which is kept as distant as possible from adjacent

metals to minimize parasitic coupling. Other on-chip components including the bootstrap drivers and gate-leakage timer are symmetrically placed in the center of the chip in order to produce an unskewed antenna radiation pattern. Two 90  $\mu$ m by 90  $\mu$ m pads (Fig. 6(h)) are also symmetrically placed on-chip, inside the loop antenna, for the input power supply.

On-chip ESD protection is a challenge for the two power-ground pads. They are connected with two back-to-back ESD protection diodes. Although one diode in this approach is forward biased, simulation showed that for  $V_{DD}$  values below 200 mV, only 175 pA of leakage current is drawn, representing only 0.6% of total power consumption.

## VI. MEASURED RESULTS

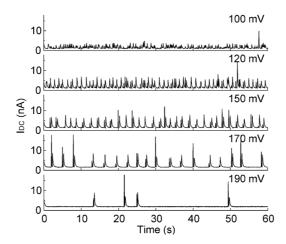

Fig. 7 shows gate-leakage timer oscillatory transients with respect to changes in  $V_{DD}$ , observed indirectly through the supply current of the full chip. Periodic peaks in the system's current consumption  $(I_{DC})$  suggest proper discharge of core multiplier deep-trench capacitors, thereby confirming timer oscillation. Oscillation is observed over the range of input supplies from 100 to 190 mV. This clock frequency  $(f_{timer})$  reaches 1 Hz at a  $V_{DD}$  of 130 mV and inversely scales with voltage with a rate of  $\sim$ 1 Hz/20 mV, agreeing with simulations. Each peak represents the timer's transition from discharge-state to charge-state.

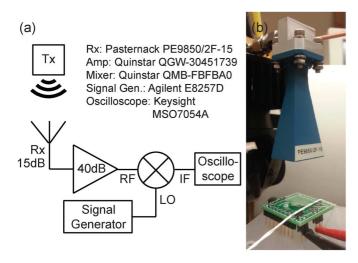

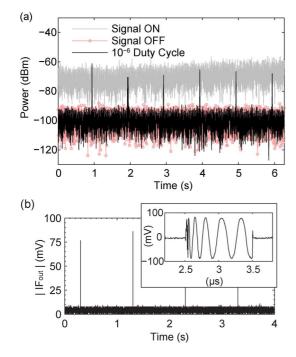

The chip's RF transmission characteristics are studied with a 15 dB horn receiver antenna 10 cm away as presented in Fig. 8. Fig. 9 presents the duty-cycled oscillation recorded both as raw RF signal with a spectrum analyzer, and an IF signal after down-converting to  $\sim$ 3 MHz by mixing with a 32.39 GHz carrier. Fig. 9(a) shows the spectrum analyzer output of the RF signal sampled in the frequency-domain with a 500 Hz bandwidth, but plotted against the time axis. The three traces indicate oscillator states of on, off, and  $10^{-6}$  duty-cycled, respectively. The data confirms that the duty-cycled signal power level toggles between that of on- and off-states. Fig. 9(b) shows the same signal mixed to baseband using the setup in Fig. 8(a). The inset is a zoomed-in view of a single radiation pulse, showing that the LC oscillator transient reaches steady-state within the 1  $\mu$ s pulse width.

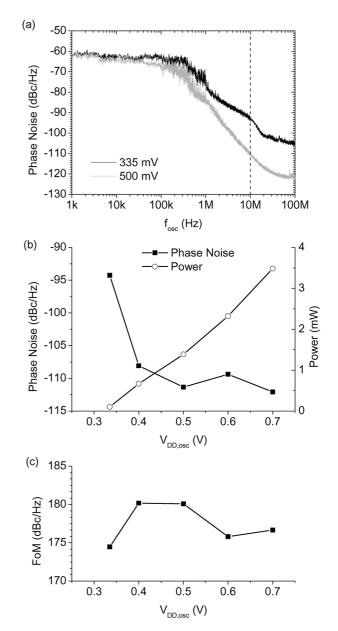

Fig. 10(a) shows the measured phase noise of the 33.1 GHz oscillator at supply voltages of 335 mV (which is near the supply voltage provided by the voltage multiplier during pulsed operation) and 500 mV. At 10 MHz offset, the phase noise is

Fig. 8. (a) Schematic of RF measurement setup and (b) picture of horn receiver antenna at 10 cm transmission distance.

Fig. 9. Time-domain waveforms of (a) receiver output (RF) of 32.29 GHz oscillator monotonously-on, monotonously-off (noise floor), and  $10^{-6}$  duty-cycled; (b) RF mixed to baseband (IF) with inset showing the zoom-in of a single peak. Measurements taken for  $V_{DD,osc}=300~{\rm mV}$ .

-94.24 and -111.34 dBc/Hz, respectively. Fig. 10(b) shows the phase noise at 10 MHz offset across different supply voltages as well as the power consumption. It can be seen that phase noise generally improves with supply voltage. A popular figure of merit (FoM) that captures the trade-off between phase noise and power dissipation is  $-L+20\log(\omega_o/\Delta\omega)-10\log(P_{DC}),$  where L is the phase noise in dBc/Hz at an offset  $\Delta\omega$  from the carrier frequency  $\omega_o$ . Fig. 10(c) plots the FoM versus supply voltage. At a supply voltage of 335 mV, the power consumption is 0.104 mW and the FoM achieved is 174.5 dBc/Hz. At 500 mV, the FoM improves to 180.1 dBc/Hz.

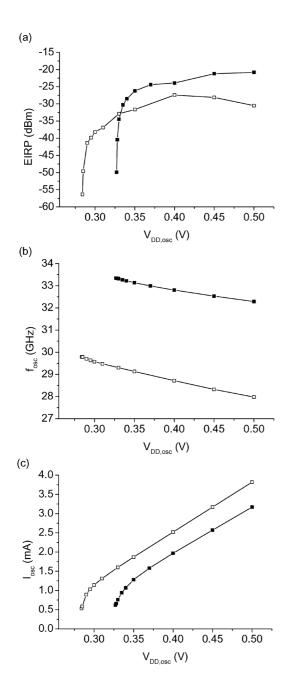

The oscillator startup behavior as a function of bias voltage is characterized in Fig. 11, for modules designed for both 29- and 33-GHz  $f_{osc}$  operation. CW EIRP of -49.89 dBm and -56.40 dBm are achieved at oscillator startup voltages  $(V_{DD,osc})$  of

Fig. 10. (a) Oscillator phase noise at startup (335 mV) and higher (500 mV) supply voltages; (b) 10 MHz-offset phase noise and power; and (c) FoM across different  $V_{DD,osc}$  levels.

0.284 V and 0.327 V for the 29 GHz and 33 GHz designs, respectively. Relatively low CW EIRP values are caused by the small dc power consumption of the oscillator and extremely small size of the antenna. EIRP for the 33 GHz module increases to -20.83 dBm at 0.5 V  $V_{DD,osc}$ .

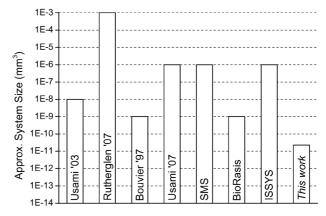

Table I compares the performance of the transmitter with Pellerano  $et\ al.$ , an RFID chip operating at 45 GHz [11]. The energy consumed per transmitted bit is comparable between the two designs ( $\sim 3\ nJ/b$ ), while we use only about 7% of the area (this number will only decrease when including the antenna size of Pellerano  $et\ al.$ , which has not been stated) and dc power that is more than three orders of magnitude smaller (but at 5000 times lower bit rate). Table I compares the designs using (bit — energy  $\times$  area)<sup>-1</sup> as a second FoM, again, not including the antenna size of Pellerano  $et\ al.$  Fig. 12 reports the size of our system in comparison with other reported small wireless systems previously developed [20], showing our design to

Fig. 11. RF oscillator characteristics of (a) EIRP, (b)  $f_{osc}$ , and (c)  $I_{osc}$  for 33 GHz (closed) and 29 GHz (open) designs versus  $V_{DD,osc}$  (Fig. 4(g)). Measured = from a single die.

be more than one order of magnitude smaller by volume than any previously reported radio design.

# VII. VARIABILITY

Stringent power and voltage conditions give rise to large performance variations in both the millimeter-wave oscillator and its control circuitry. The sensitivity of the oscillator's EIRP, dc power consumption, and carrier frequency with respect to  $V_{DD,osc}$  (Fig. 11) makes it difficult to predict exact carrier frequencies. This requires careful sweeping of the narrow receiver bandwidth (<10 kHz) to find the carrier.

Current-starved buffer chains in the control circuit introduce timing variations that directly affect the amount of transmitted power. The gate-leakage timer frequency (Fig. 13(a)) is especially prone to mismatch variations, due to sensitivity of Schmitt trigger threshold levels in the ultra-subthreshold region. The

TABLE I

TRANSMITTER SPECIFICATIONS

|                                            | This work                                        | Pellerano et al. [11]*                           |

|--------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Carrier frequency                          | 33 GHz                                           | 45 GHz                                           |

| System area                                | $0.3 \times 0.3 \text{ mm}^2$ (antenna included) | $1.3 \times 0.95 \text{ mm}^2$ (without antenna) |

| Reading dist.<br>(equivalent 13<br>dB SNR) | 12.7 cm**                                        | 1.3 cm***<br>(10 <sup>-3</sup> BER)              |

| dc input power                             | 3.1 nW                                           | $> 19 \mu W$                                     |

| Bit rate                                   | 1 bps                                            | 5 kbps                                           |

| Energy cost per bit                        | ~3.1 nJ                                          | > 3.8 nJ                                         |

| FoM,<br>(bit-energy×area) <sup>-1</sup>    | 3.6 nJ <sup>-1</sup> mm <sup>-2</sup>            | $< 0.2 \text{ nJ}^{-1}\text{mm}^{-2}$            |

- \* Values obtained/calculated based on input power of 2 dBm.

- \*\* Measured with 15 dB receiver antenna gain.

- \*\*\* Calculated for 3 dB receiver antenna gain.

Fig. 12. System size comparison, antennas included, with other small radios: reproduced from [20]. From left, [21]–[24], and next three cited from [20].

varied durations of the gate-leakage-timer clock lead to varied durations in the oscillator discharge events, resulting in widely distributed bit rates across chips. An excessively high bit rate prevents deep-trench capacitors from charging fully, resulting in lower transmitted power.

Fig. 13(b) shows that oscillator discharge events occur across a wide range of peak locations and amplitudes. Timing uncertainty in the delay buffer chain (Fig. 4(b)) causes peaks to occur at different times. Longer idle time before the discharge leads to more leakage through CMOS switches, resulting in smaller values of  $I_{osc}$ . This is confirmed by the histograms in Fig. 14; there is a particularly large functionality variation in  $f_{timer}$  and average system power consumption. Among the 80 dice tested, a total of 18 pulsed with an expected clock frequency of  $\sim$ 1 Hz. Thirteen of these showed complete functionality. The rest lost functionality due to either insufficient ESD protection or PVT variations. The number of functional chips increased at higher supply voltages and power levels.

# VIII. CONCLUSION

In this work, we explored the limits of power, voltage, and size in the design of a radio transmitter. Achievable power levels are limited by subthreshold leakage, operating voltages by 4kT/q, and size by the thermal noise floor at the receiver. Voltages and power levels are chosen to match those available

Fig. 13. 30 runs of Monte Carlo simulations showing timing uncertainty in (a) period of gate leakage timer, and (b) peak location and magnitude of antenna discharge current transients.

Fig. 14. Chip-to-chip performance distribution across 13 samples, with corresponding median values.  $V_{startup}$  is the lowest value of  $V_{DD,osc}$  to achieve 10 dB SNR at 10 cm reading distance. The histogram for average power has the benefit of 18 samples.

from biological transmembrane potentials. The goal of this effort was to explore the possibility of making a radio transmitter small enough and low-power enough to be powered by a single cell.

Extreme duty cycling (by a factor of  $10^{-6}$ ) and sub-Hz data transmission rates are key power-saving features of the design. Limitations in available power dictate simple modulation approaches, such as on-off keying or pulse-position modulation. In this prototype, the time interval between pulses carries information on the amount of power harvested by the radio. The ability to support on-off keying can be included with a single switch designed to be triggered by an electrochemical reaction. The seemingly low data rate of 1 bps is sufficient in monitoring

biological processes, a considerable fraction of which change over much longer time scales.

Practical limitations in the design of a sub-millimeter-scale radio were also considered. Quality factor of on-chip passives limit duty-cycling and switched capacitor circuit efficiencies. Process variations have significant effects on the transmitter performance. To achieve yields greater than 25%, we had to operate at higher nominal voltages and power levels. Although the design has room for further optimization, the sensitivity of the Schmitt trigger/switched capacitor cascade against supply voltage levels and transistor mismatch entail a practical limit for performance yield. A mass deployment scheme is suggested to solve such uncertainty, which also takes full advantage of the extremely small system size and biological-level power density of the transmitter.

### ACKNOWLEDGMENT

The authors thank Jared Roseman, Haig Norian, Steven Warren, Kevin Tien, and Jin Zhou of Columbia University for their assistance in circuit design, simulation, and chip post-processing.

### REFERENCES

- [1] K. Shepard, T. Ito, and A. J. Griffith, "Extracting energy from the inner ear," *Nature Biotechnology*, vol. 30, no. 12, pp. 1204–1205, 2012.

- [2] N. Lane and W. Martin, "The energetics of genome complexity," Nature, vol. 467, no. 7318, pp. 929–934, 2010.

- [3] R. Landauer, "Irreversibility and heat generation in the computing process," *IBM Journal of Research and Development*, vol. 5, no. 3, pp. 183–191, 1961.

- [4] R. Gonzalez, B. M. Gordon, and M. A. Horowitz, "Supply and threshold voltage scaling for low power cmos," *Solid-State Circuits*, *IEEE Journal of*, vol. 32, no. 8, pp. 1210–1216, 1997.

- [5] J. Burr and A. M. Peterson, "Ultra low power cmos technology," in NASA VLSI Design Symposium, Citeseer, 1991, vol. 4, no. 1, pp. 4–2.

- [6] B. H. Calhoun, A. Wang, and A. Chandrakasan, "Modeling and sizing for minimum energy operation in subthreshold circuits," *Solid-State Circuits*, *IEEE Journal of*, vol. 40, no. 9, pp. 1778–1786, 2005.

- [7] J. D. Meindl, "Low power microelectronics: Retrospect and prospect," Proceedings of the IEEE, vol. 83, no. 4, pp. 619–635, 1995.

- [8] C. A. Balanis, Antenna Theory: Analysis and Design. : John Wiley & Sons, 2012.

- [9] Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor. : Oxford Univ. Press, 2011.

- [10] M. Usami, "An ultra-small rfid chip: μ-chip," in Advanced System Integrated Circuits, 2004 Proceedings of 2004 IEEE Asia-Pacific Conference on, 2004, pp. 2–5, IEEE.

- [11] S. Pellerano, J. Alvarado, and Y. Palaskas, "A mm-wave power-har-vesting rfid tag in 90 nm cmos," *Solid-State Circuits, IEEE Journal of*, vol. 45, no. 8, pp. 1627–1637, 2010.

- [12] F. Gutierrez, S. Agarwal, K. Parrish, and T. S. Rappaport, "On-chip integrated antenna structures in cmos for 60 ghz wpan systems," Selected Areas in Communications, IEEE Journal on, vol. 27, no. 8, pp. 1367–1378, 2009.

- [13] S. Emami, R. F. Wiser, E. Ali, M. G. Forbes, M. Q. Gordon, X. Guan, S. Lo, P. T. McElwee, J. Parker, and J. R. Tani et al., "A 60 ghz cmos phased-array transceiver pair for multi-gb/s wireless communications," in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011 IEEE International, 2011, pp. 164–166, IEEE.

- [14] M. Tabesh, J. Chen, C. Marcu, L. Kong, S. Kang, A. M. Niknejad, and E. Alon, "A 65 nm cmos 4-element sub-34 mw/element 60 ghz phased-array transceiver," *Solid-State Circuits, IEEE Journal of*, vol. 46, no. 12, pp. 3018–3032, 2011.

- [15] J. Sharma and H. Krishnaswamy, "216-and 316-ghz 45-nm soi cmos signal sources based on a maximum-gain ring oscillator topology," *Microwave Theory and Techniques, IEEE Trans.*, vol. 61, no. 1, pp. 492–504, 2013.

- [16] K. W. Kim and Y. Rahmat-Samii, "Handset antennas and humans at ka-band: The importance of directional antennas," *Antennas and Prop*agation, IEEE Trans., vol. 46, no. 6, pp. 949–950, 1998.

- [17] C. P. Yue and S. S. Wong, "On-chip spiral inductors with patterned ground shields for si-based rf ics," *Solid-State Circuits, IEEE Journal* of, vol. 33, no. 5, pp. 743–752, 1998.

- [18] Y.-S. Lin, D. Sylvester, and D. Blaauw, "A sub-pw timer using gate leakage for ultra low-power sub-hz monitoring systems," in *Custom Integrated Circuits Conference*, 2007. CICC'07. IEEE, 2007, pp. 397–400. IEEE.

- [19] C. Liang and B. Razavi, "A layout technique for millimeter-wave pa transistors," in *Radio Frequency Integrated Circuits Symposium* (RFIC), 2011 IEEE, 2011, pp. 1–4, IEEE.

- [20] P. Burke and C. Rutherglen, "Towards a single-chip, implantable rfid system: Is a single-cell radio possible?," *Biomedical Microdevices*, vol. 12, no. 4, pp. 589–596, 2010.

- [21] M. Usami, A. Sato, K. Sameshima, K. Watanabe, H. Yoshigi, and R. Imura, "Isscc 2003/session 22/td: Embedded technologies/paper 22.7," 2003

- [22] C. Rutherglen and P. Burke, "Carbon nanotube radio," *Nano Letters*, vol. 7, no. 11, pp. 3296–3299, 2007.

- [23] J. Bouvier, Y. Thorigne, S. A. Hassan, M. Revillet, and P. Senn, "A smart card cmos circuit with magnetic power and communication interface," in *Solid-State Circuits Conference*, 1997. Digest of Technical Papers. 43rd ISSCC., 1997 IEEE International, 1997, pp. 296–297, IEEE.

- [24] M. Usami, H. Tanabe, A. Sato, I. Sakama, Y. Maki, T. Iwamatsu, T. Ipposhi, Y. Inoue, and T. Hitachi, "A  $0.05\times0.05~\text{mm}^2$  rfid chip with easily scaled-down id-memory," in *ISSCC*, 2007, pp. 482–483.

Jaebin Choi received the B.S. degree magna cum laude in applied and engineering physics from Cornell University, Ithaca, NY, in 2011 and the M.S. degree in electrical engineering from Columbia University, New York, NY, in 2012. As a Ph.D. candidate he carried out research in low-voltage, low-power circuit design for implantable systems under the supervision of Prof. Kenneth L. Shepard. Currently he is working as Researcher in the Sensor Systems Research Center at the Korea Institute of Science and Technology, Seoul, Korea. His current

research interests include interfacing electrical and biological systems for sensing and powering applications.

**Eyal Aklimi** is currently a Ph.D. candidate of Electrical Engineering at Columbia University in New York, working as a research assistant in the bioelectronics systems lab. Prior to his PhD, Eyal received his M.S degree in electrical engineering at Columbia University, and bachelors degree of Electrical Engineering and Physics from Tel Aviv University in Israel. His work experience includes co-founding a start-up company, and three years of experience as an engineer. His research interests includes magnetics: spintronics thin-film devices for

magnetic field sensing, and materials and methods for integrated inductors, both integrated with CMOS back-end fabrication.

Chen Shi received the B.S. degrees in Electrical Engineering and Bioengineering in 2013 from the University of Washington, Seattle, WA. He then obtained the M.S. degree in Electrical Engineering in 2014 from the Columbia University, New York, NY. He is currently a Ph.D. candidate in Electrical Engineering at Columbia University under the direction of Professor Kenneth Shepard. His research interests are analog and mixed-signal integrated circuit design for biomedical applications, including ultrasound imaging and neural interfaces.

David Tsai (M'13–SM'03) received a B.E. in software engineering, with 1st class honors, and Master of Biomedical Engineering in 2007 from the University of New South Wales, Sydney, Australia. He then received a PhD in biomedical engineering in 2012 from the same university. He is currently a NHMRC CJ Martin Postdoctoral Research Fellow jointly appointed between Electrical Engineering and Biological Sciences of Columbia University. His research activities focus on microelectronic neural interfaces, implantable bionics, computational neuroscience and

neurobiology of the visual system.

Harish Krishnaswamy (S'03–M'09) received the B.Tech. degree from the Indian Institute of Technology, Madras, India, in 2001, and the M.S. and Ph.D. degrees from the University of Southern California, Los Angeles, CA, USA, in 2003 and 2009, respectively, all in electrical engineering. In 2009, he joined the Electrical Engineering Department, Columbia University, New York, NY, USA, as an Assistant Professor.

His research interests broadly span integrated devices, circuits, and systems for a variety of RF,

mm-wave, and sub-mm-wave applications. His current research efforts are focused on silicon-based mm-wave PAs, sub-mm-wave circuits and systems, reconfigurable/broadband RF transceivers for cognitive and software-defined radio, full-duplex radios, and circuits and systems for massive mm-wave MIMO communication. His research group has received funding from various federal agencies, including NSF and DARPA, as well as industry. He also serves as a technical consultant to industry.

Prof. Krishnaswamy serves as a member of the Technical Program Committee (TPC) of several conferences, including the IEEE RFIC Symposium. He was the recipient of the IEEE International Solid-State Circuits Conference (ISSCC) Lewis Winner Award for Outstanding Paper in 2007, the Best Thesis in Experimental Research Award from the USC Viterbi School of Engineering in 2009, the Defense Advanced Research Projects Agency (DARPA) Young Faculty Award in 2011, and a 2014 IBM Faculty Award.

Kenneth L. Shepard (M'91–SM'03–F'08) received the B.S.E. degree from Princeton University, Princeton, NJ, in 1987 and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1988 and 1992, respectively. From 1992 to 1997, he was a Research Staff Member and Manager with the VLSI Design Department, IBM T. J. Watson Research Center, Yorktown Heights, NY, where he was responsible for the design methodology for IBM's G4 S/390 microprocessors.

Since 1997, he has been with Columbia University, New York, where he is now Professor of Electrical Engineering and Biomedical Engineering. He also was Chief Technology Officer of CadMOS Design Technology, San Jose, CA, until its acquisition by Cadence Design Systems in 2001. His current research interests include power electronics, carbon-based devices and circuits, and CMOS bioelectronics.

Dr. Shepard was Technical Program Chair and General Chair for the 2002 and 2003 International Conference on Computer Design, respectively. He has served on the Program Committees for IEDM, ISSCC, VLSI Symposium, ICCAD, DAC, ISCAS, ISQED, GLS-VLSI, TAU, and ICCD. He received the Fannie and John Hertz Foundation Doctoral Thesis Prize in 1992, a National Science Foundation CAREER Award in 1998, and the 1999 Distinguished Faculty Teaching Award from the Columbia Engineering School Alumni Association. He has been an Associate Editor of IEEE TRANSACTIONS ON VERY LARGE-SCALE INTEGRATION (VLSI) Systems and is currently an Associate Editor for the IEEE Journal of Solid-state Circuits and IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS.