Intro

Welcome to the home page of EE6350 VLSI Design Lab for Spring 2016.

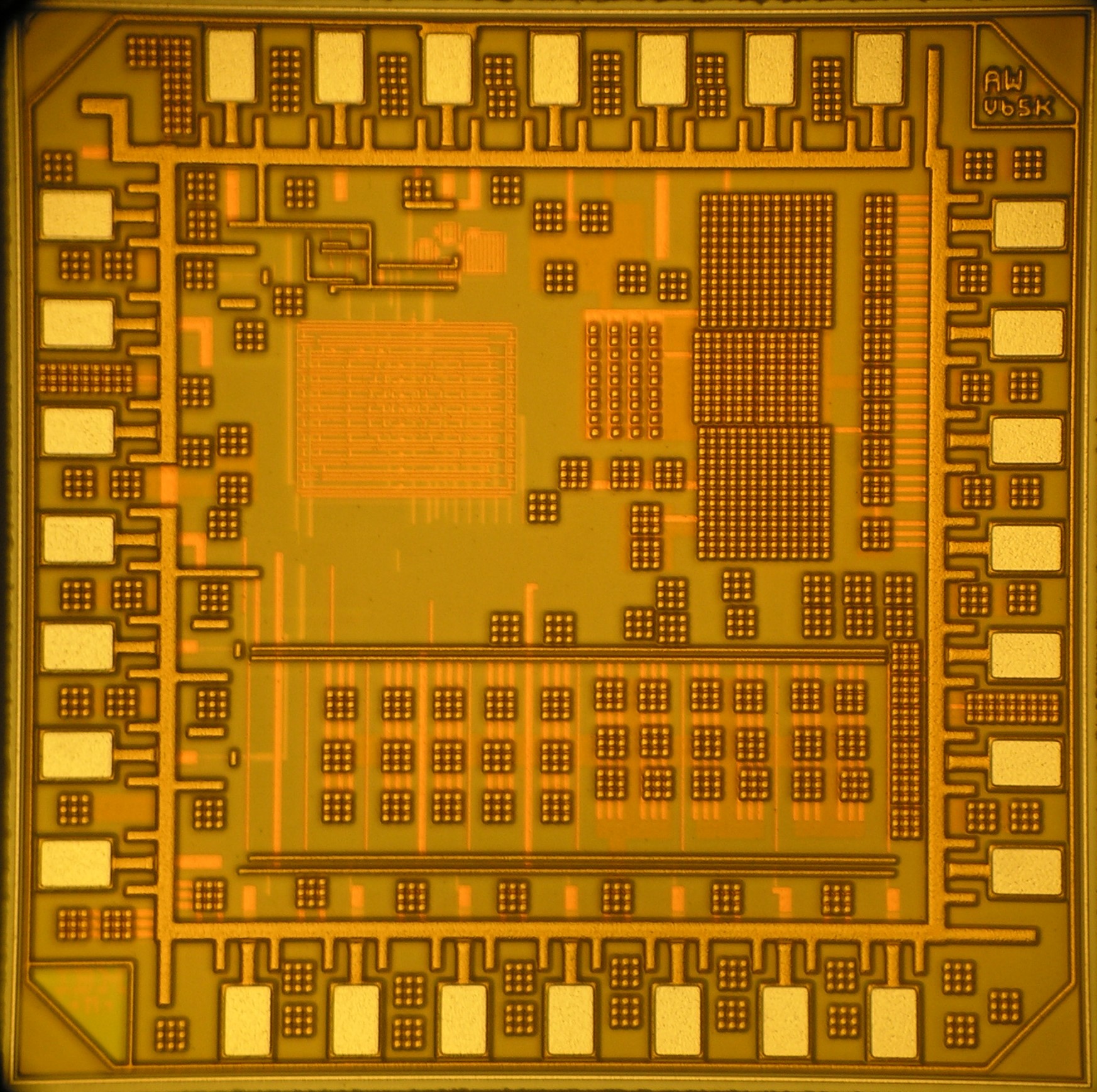

This graduate course focuses on the design, simulation, layout, verification and tape-out of an IC design. MOSIS is offering access to an Global Foundries (formerly IBM) 0.13um CMOS technology for this course. MOSIS fabricates the chips that students subsequently test.

The lead TA for the course is Vivek Mangal. The second TA for the course is Yang Xu.

Please see below for the Project Reports and

Videos

Spring 2016 Project Reports and Videos

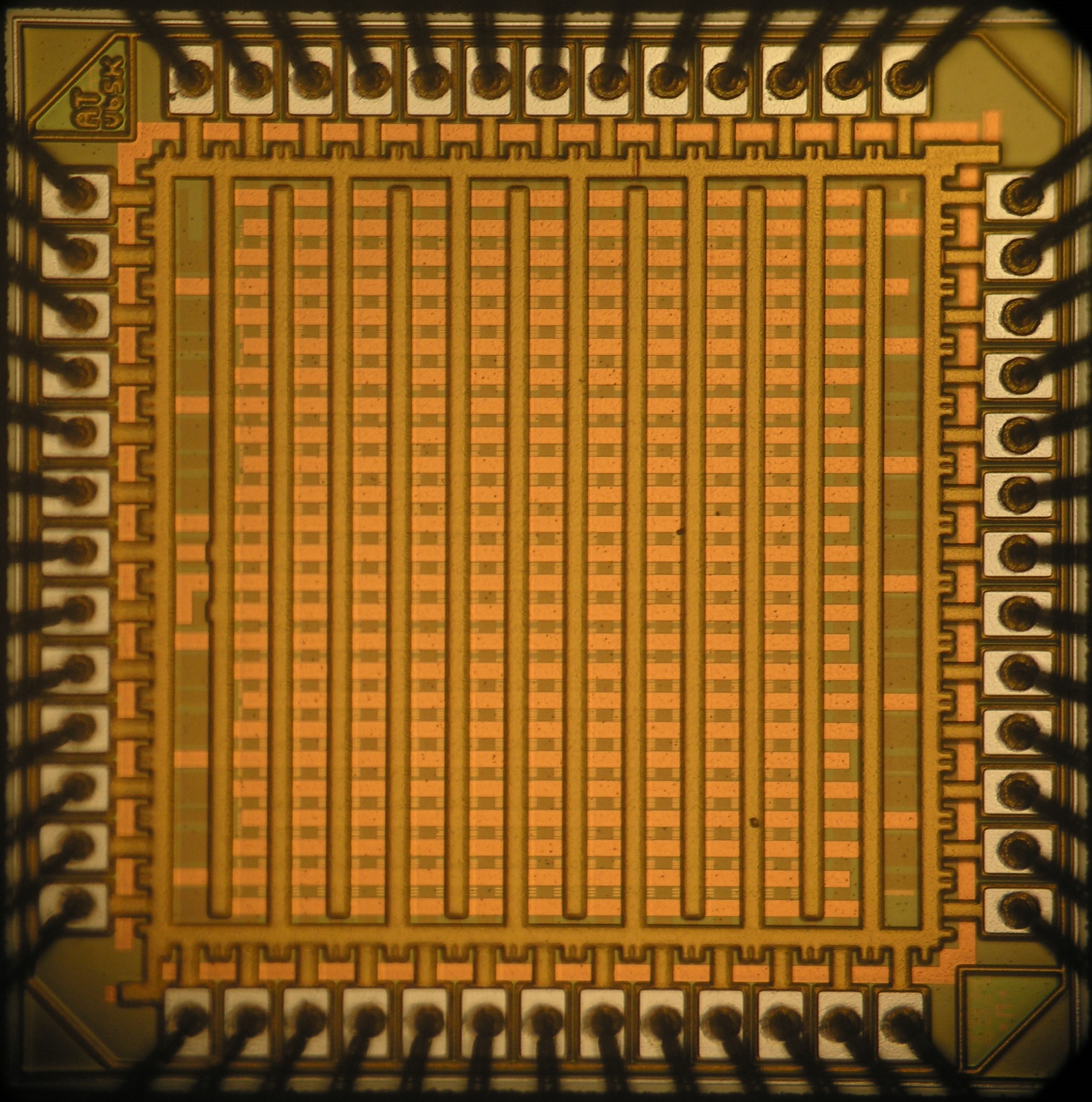

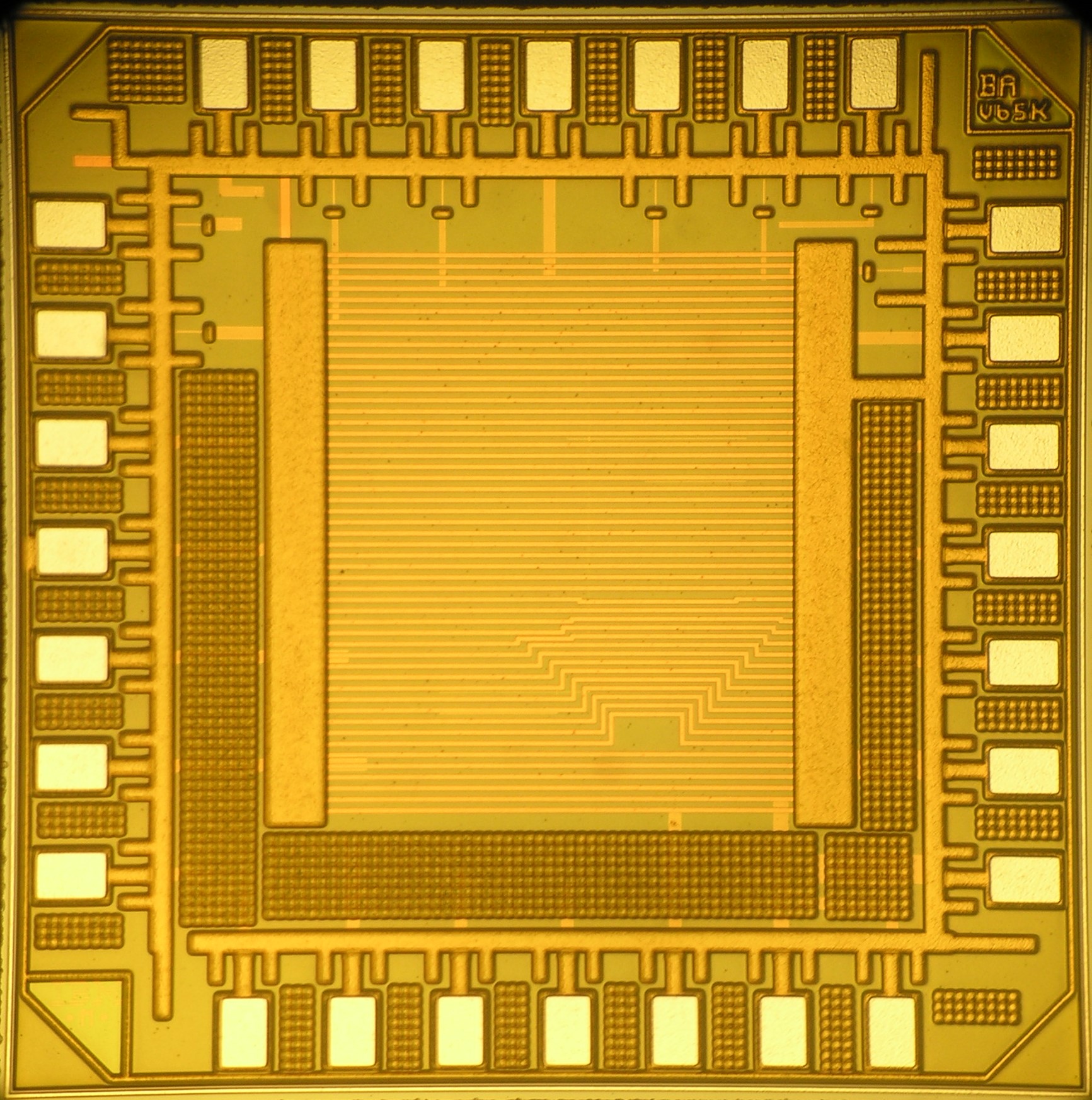

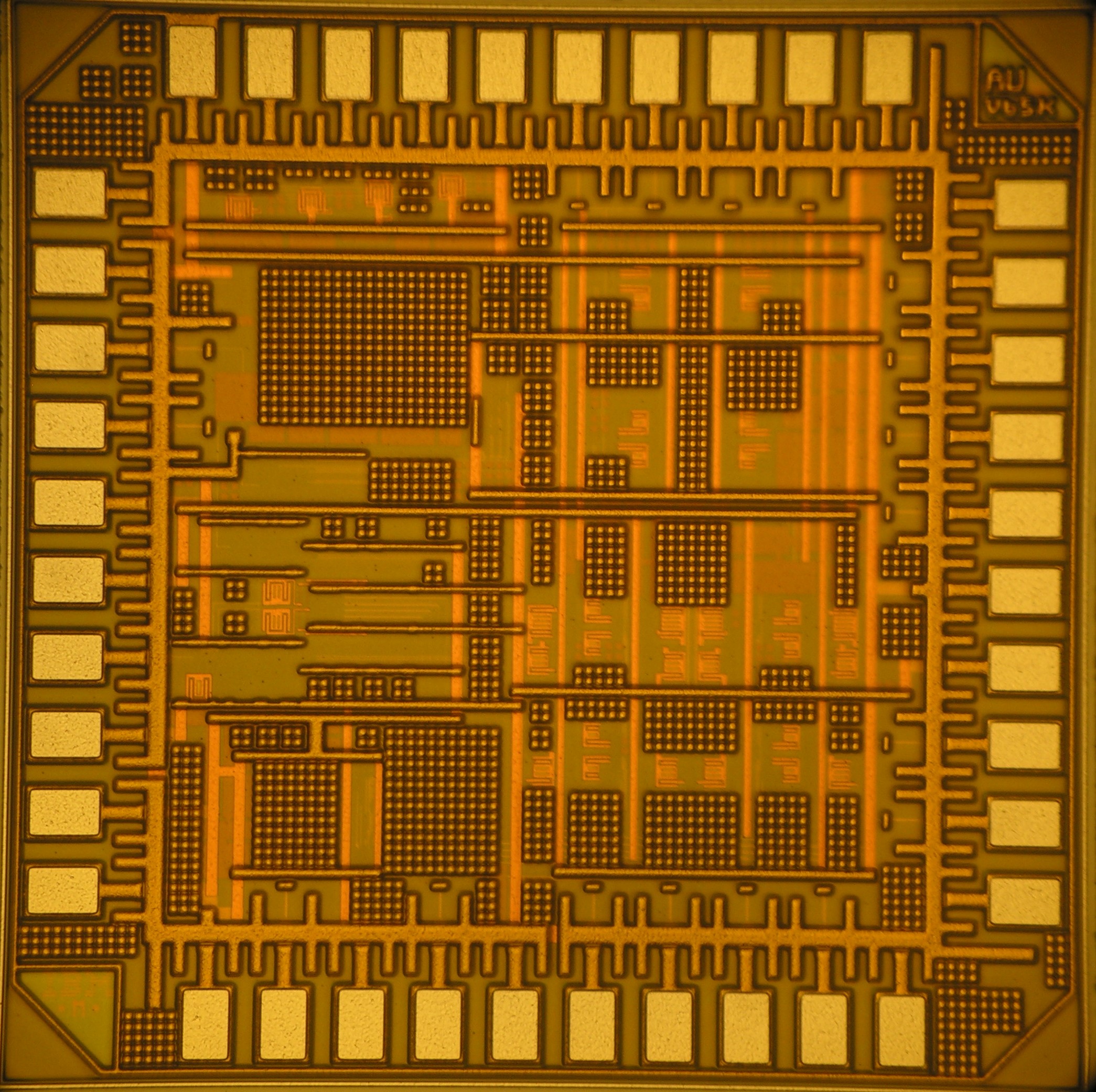

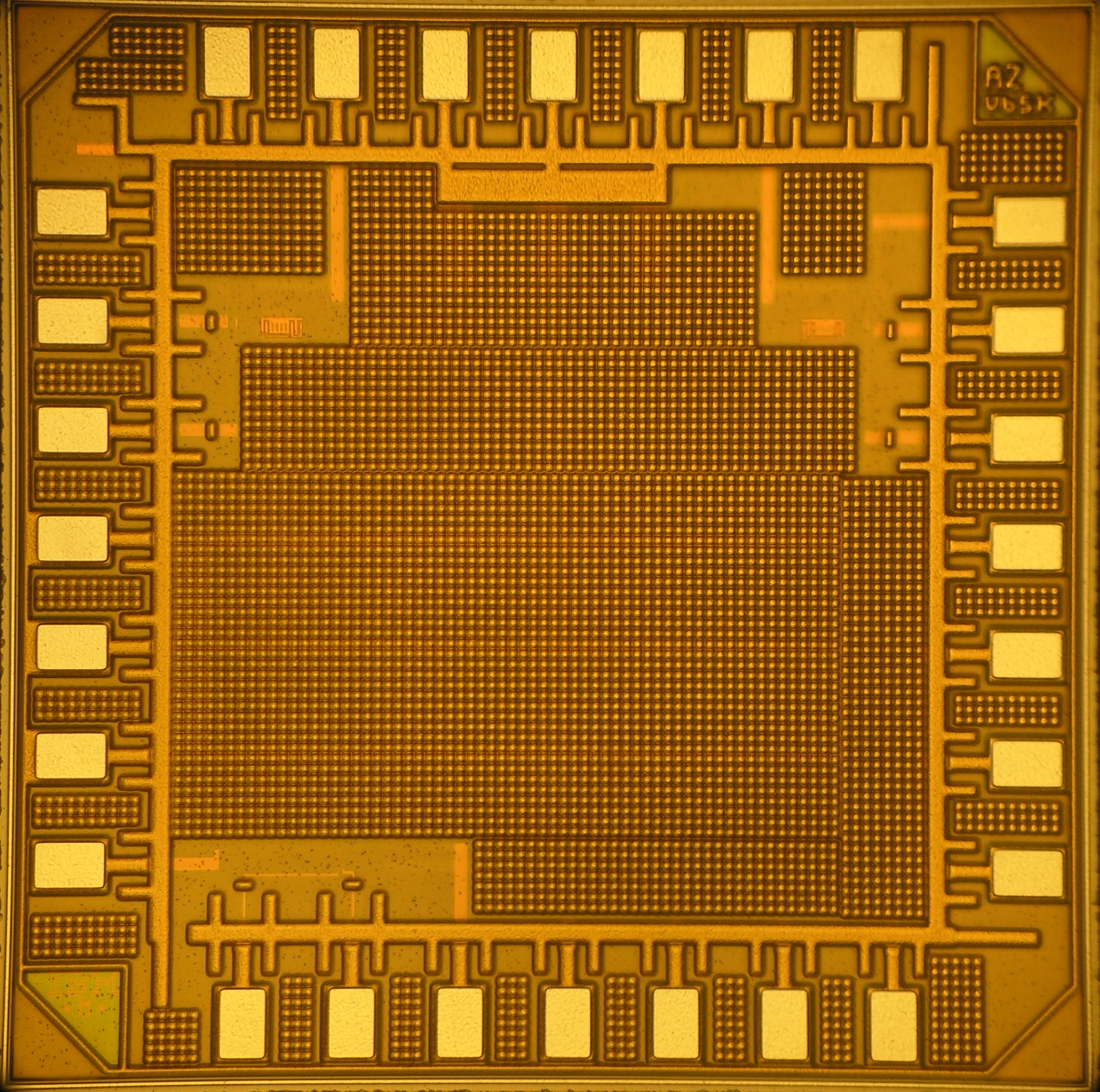

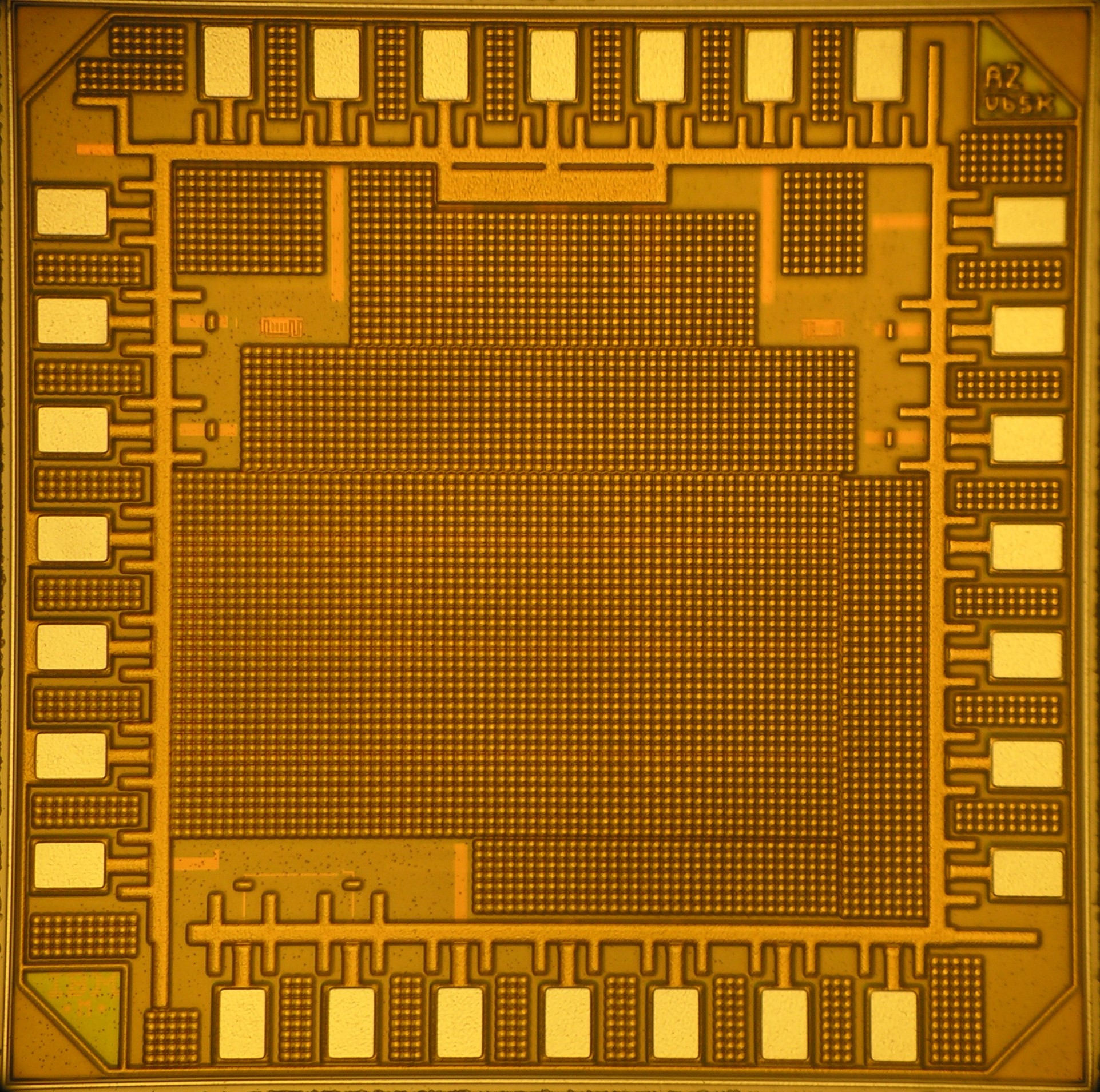

Trollstigen FPGA

Guanshun Yu, Tom Y. Cheng, Blayne Kettlewell, Harrison Liew, Mingoo Seok, and Peter Kinget, "FPGA with Improved Routability and Robustness in 130nm CMOS with Open-Source CAD Targetability," arXiv:1712.03411 [cs], Dec. 2017, [Online]. Available: http://arxiv.org/abs/1712.03411">

|

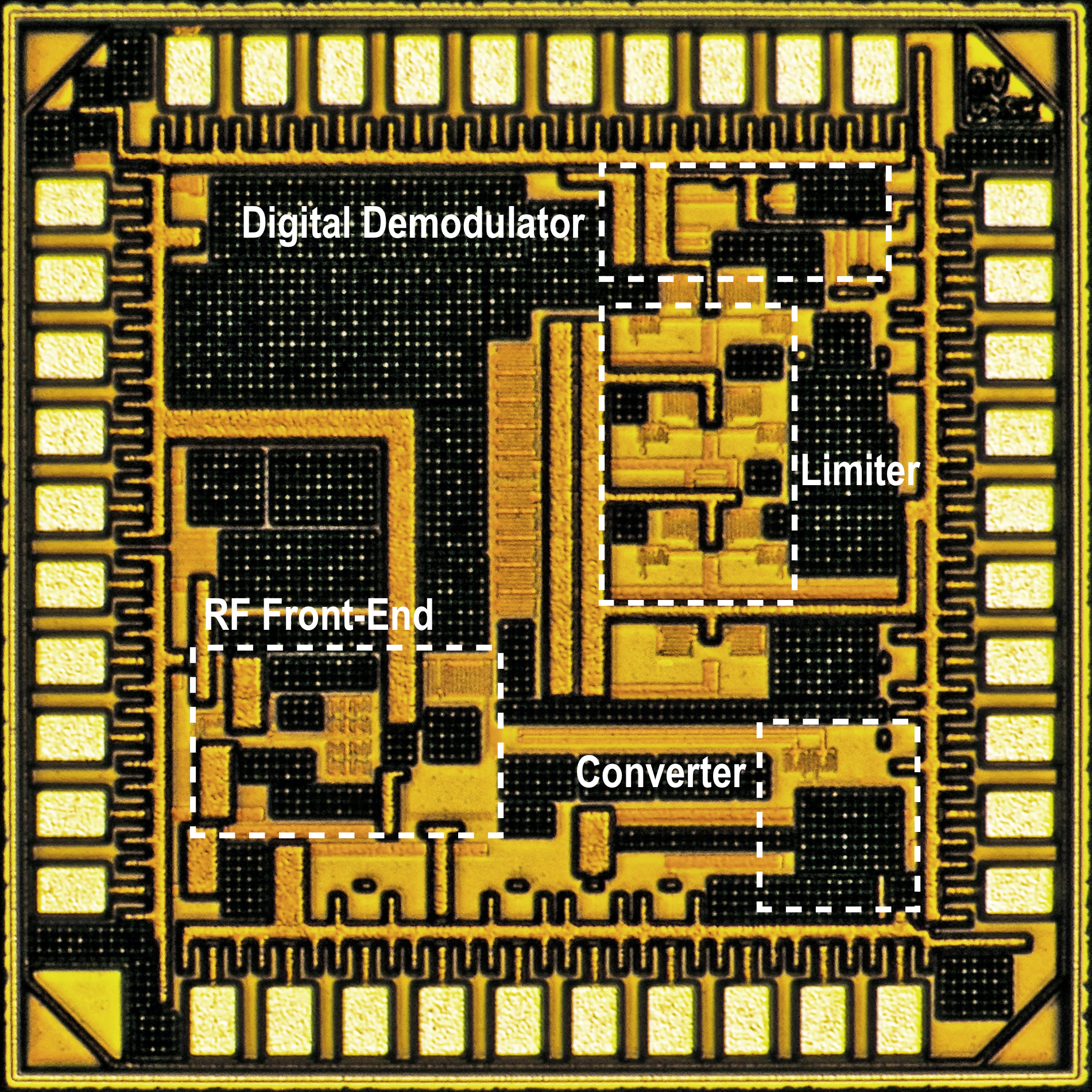

Sub-mW FM Receiver

Guoxiang Han and Nanyu Zeng

|

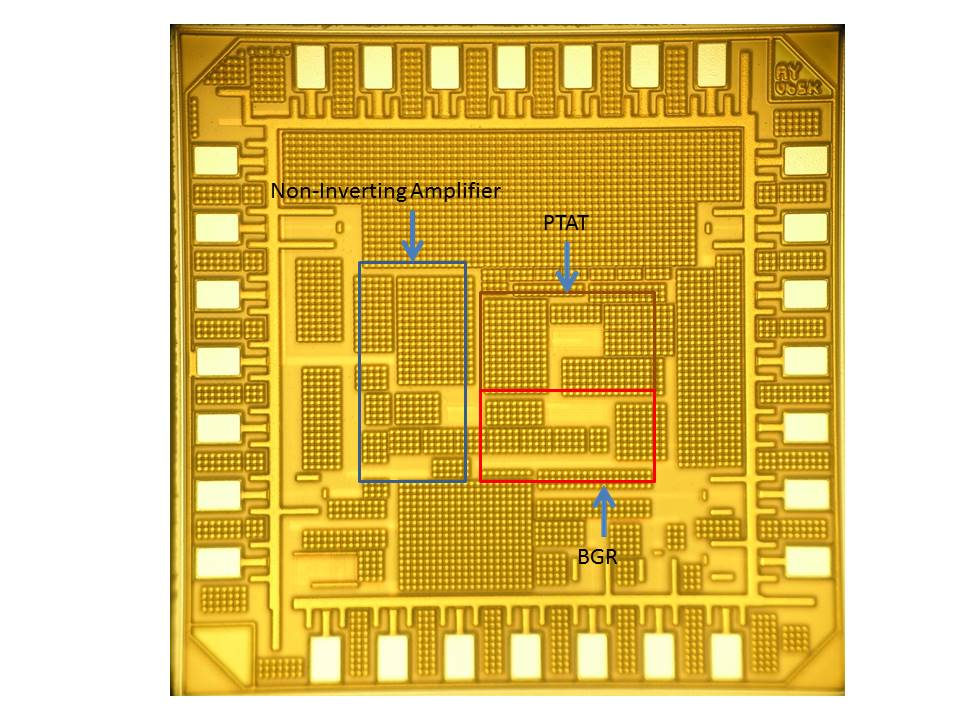

Temperature Sensor

Sukanya Sagarika Meher and Vani Alamkrutha Mogili

|

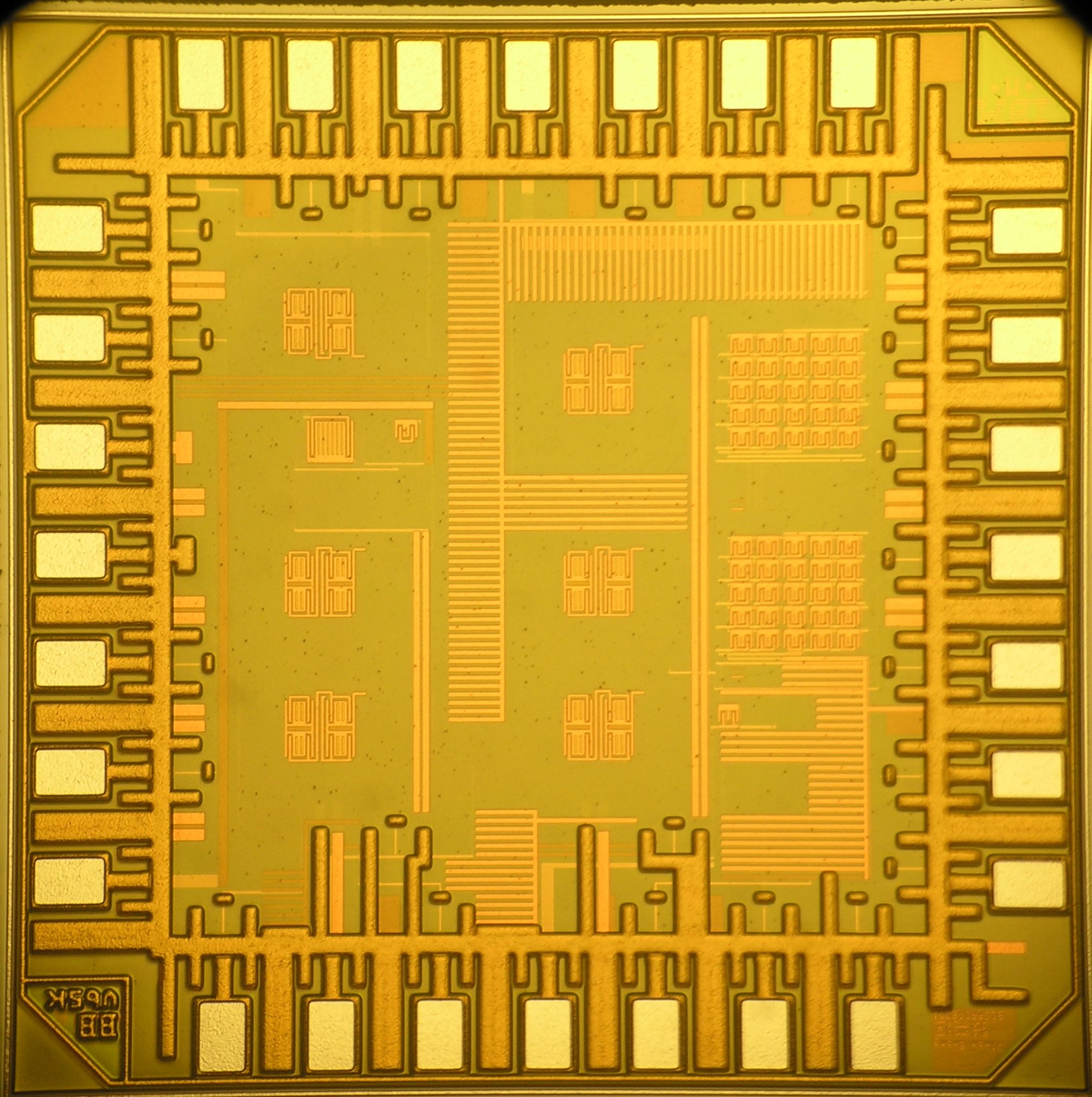

Low-Noise Current Amplifier for Electrochemical Measurements

Yihan Zhang

|

Digital Clock

Srinidhi Srinivasan and Georgios Charitos

|

RF Front End for Direct Conversion Receiver

Hao Hu and Tuo Yu

|

Photoplethysmogram (PPG)-based heart-rate monitor

Ao Li and Wantong Li

|

Digital Clock

Astha Agrawal, Jai Sharma, and Jeffrey Yuan

|

8-Bit SAR ADC

Dhruv Aggarwal, Gurkaranjot Singh Kalra, Shikhar Kwatra

|

Class-D Audio Amplifier

Suhas Rao

|