Introduction

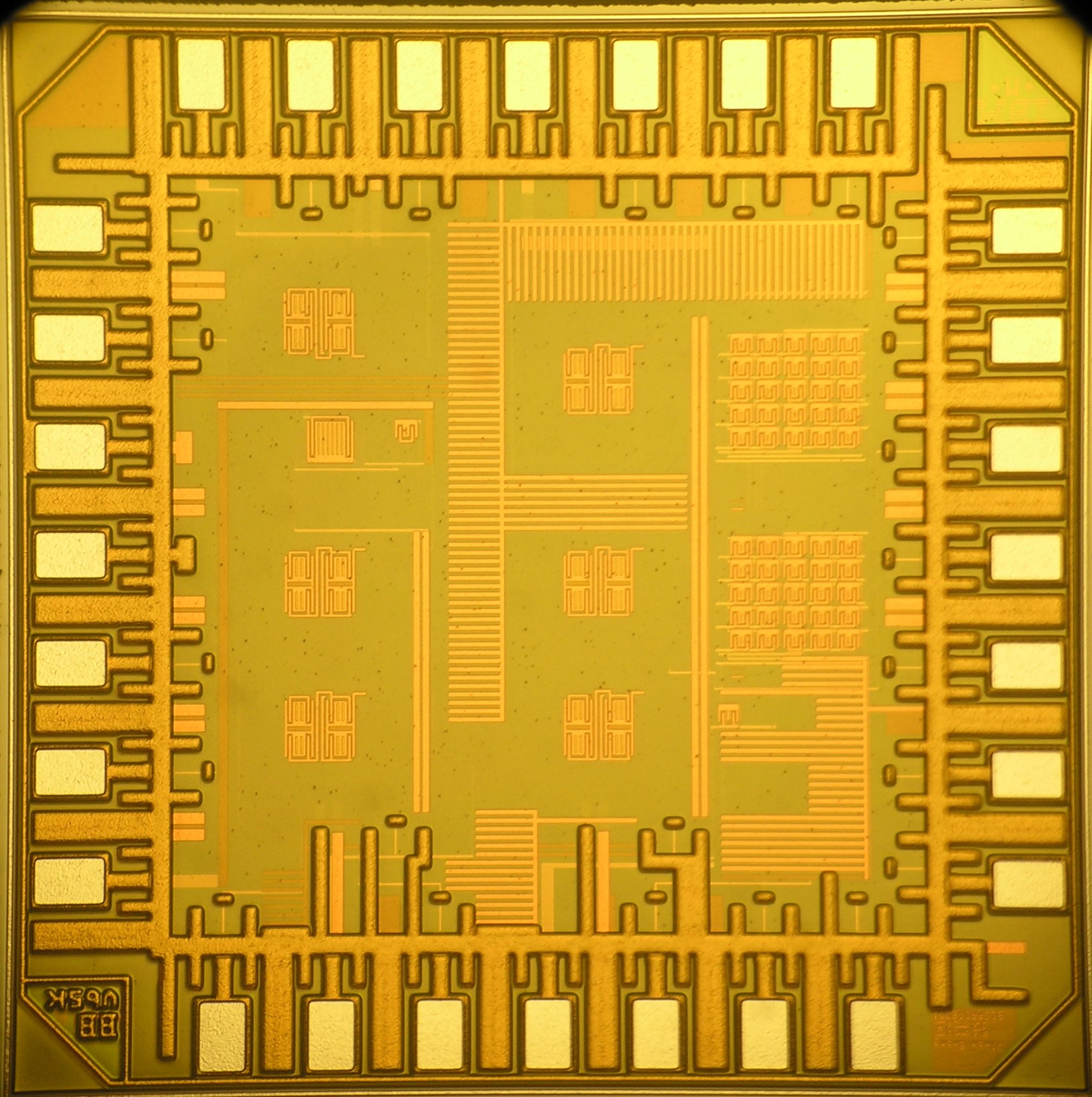

This document presents a design of low noise current amplifier using integrater and correlated double sampling techniques, as part of the EE6350 VLSI Design Lab course offered by Prof. Peter Kinget during Spring 2016. This project was made possible by the generous contribution of MOSIS, where the IC was fabricated under educational program provided, and the Electrical Engineering Department of Columbia University.