## **MO2B-2**

#### A Simplified CMOS FET Model using Surface Potential Equations For Inter-modulation Simulations of Passive-Mixer-Like Circuits

#### M. Baraani Dastjerdi and H. Krishnaswamy CoSMIC Lab,

Columbia University, New York, United States

MO2B-2

## Outline

- Motivation and Prior Art

- Simplified Surface Potential Model

- Short-Channel Effects

- Simulation and Measurement Results

- Conclusion

## Outline

- Motivation and Prior Art

- Simplified Surface Potential Model

- Short-Channel Effects

- Simulation and Measurement Results

- Conclusion

Connecting Minds. Exchanging Ideas.

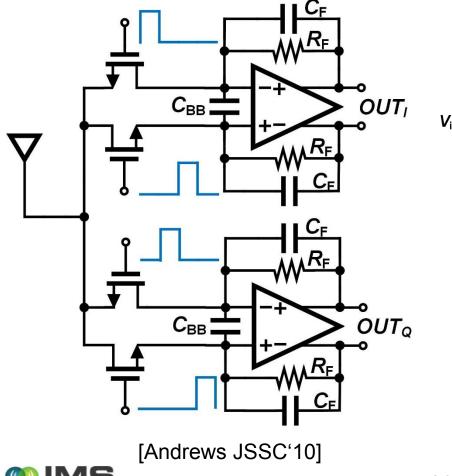

## **Circuits That Use FETs As Switches**

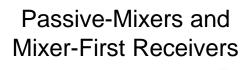

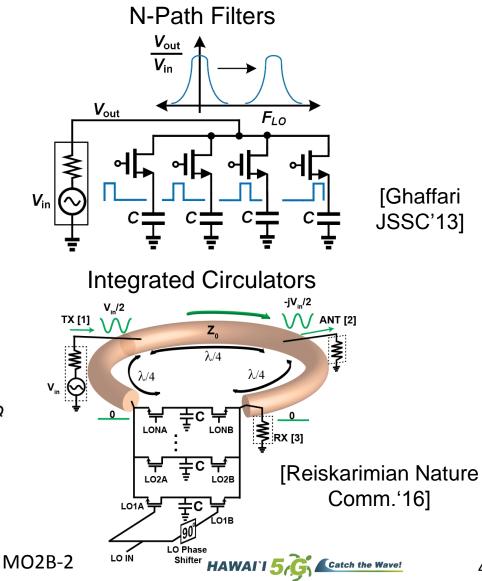

## Mixer-First Receiver Design Challenges

- Increasing switch FETs size improves linearity at the cost of power consumption.

- Increasing series resistance  $R_M$  improves linearity at the cost of NF.

consumption is calculated for an operating frequency of 1GHz.

# Linearity simulations are critical during the design phase for the optimization of passive mixer-like circuits.

## **FET Operation As a Switch**

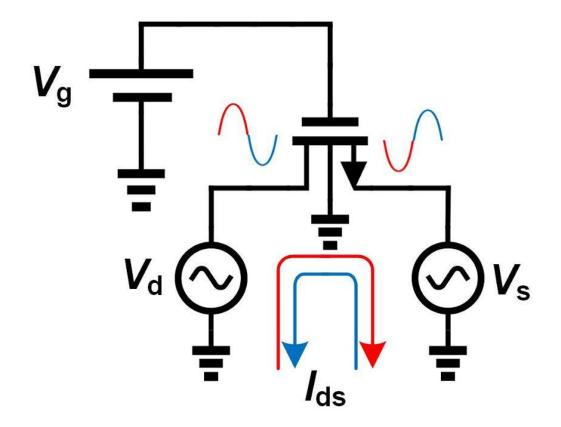

MOSFET switches are symmetric devices and typically experience source-drain reversal during AC operation.

## **Gummel Symmetry Test In BSIM4**

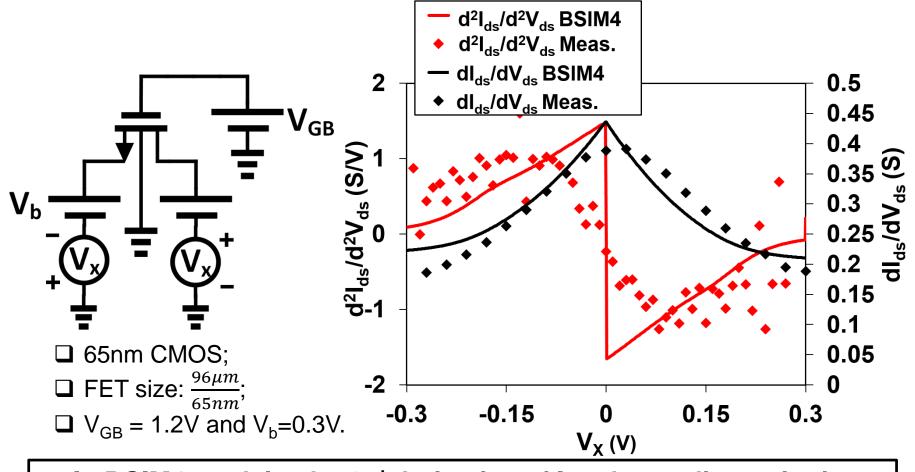

In BSIM4 models, the  $2^{nd}$  derivative of  $I_{DS}$  shows discontinuity around  $V_{DS}=0$ .

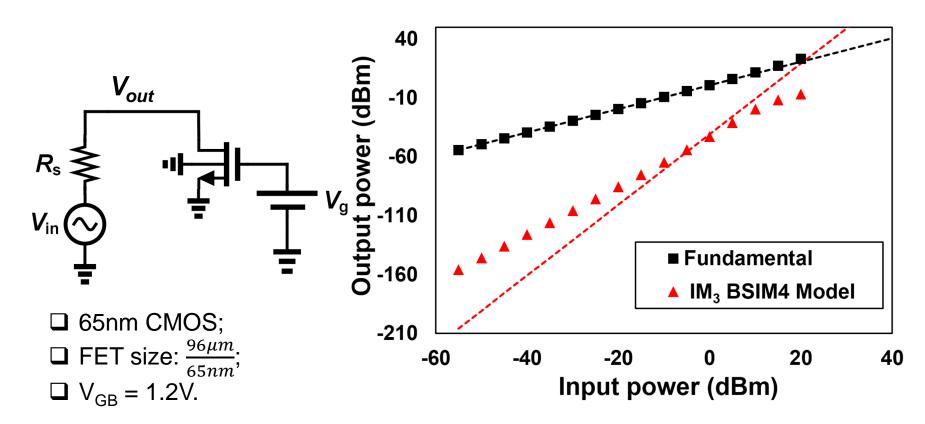

## **Two-Tone Test Using BSIM4 Model**

# The IM<sub>3</sub> predicted by BSIM4 models shows unphysical characteristics (slope of 2dB/dB).

## **Transistor Models Comparison**

| Source-referenced models<br>E.g. BSIM                 | Body-referenced models<br>E.g. PSP        |

|-------------------------------------------------------|-------------------------------------------|

| ✓ Physical driving forces are $V_{GS}$                | ✓ Symmetry is appealing.                  |

| and V <sub>DS</sub> .                                 | ✓ Effective mobility is well              |

| $\checkmark$ V <sub>T</sub> appears in the equations. | handled.                                  |

| ✓ Velocity saturation is easy to                      | $\checkmark$ It is easy to make the drain |

| handle.                                               | current continuous at V <sub>DS</sub> =0. |

| × Asymmetric around the                               | × Not provided by most digitally-         |

| source-drain reversal point.                          | driven foundries.                         |

|                                                       |                                           |

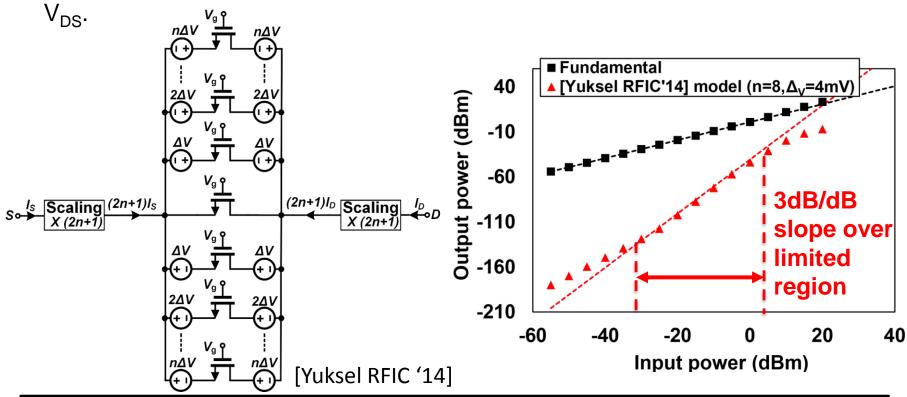

## **Prior Work**

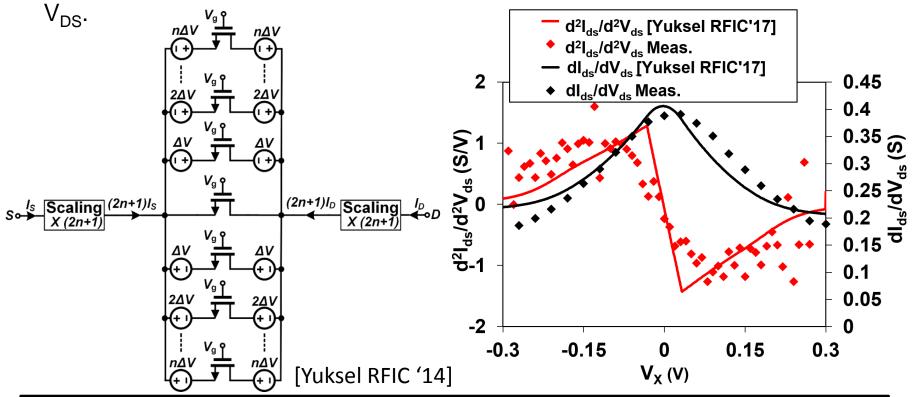

• Break the transistor into 2n+1 transistors in parallel with small offset voltages in

× High processing load (if n=32, 1 FET is replaced by 65 FET). × Predicts 3dB/dB for IM<sub>3</sub> only for  $\Delta V < V_{DS} < n\Delta V$ . × Need measurements to extract value of  $\Delta V$ .

## **Prior Work**

• Break the transistor into 2n+1 transistors in parallel with small offset voltages in

- × High processing load (if n=32, 1 FET is replaced by 65 FET). × Predicts 3dB/dB for IM<sub>3</sub> only for  $\Delta V < V_{DS} < n\Delta V$ .

- K Need measurements to extract value of  $\Delta V$ .

## Outline

- Motivation and Prior Art

- Simplified Surface Potential Model

- Short-Channel Effects

- Simulation and Measurement Results

- Conclusion

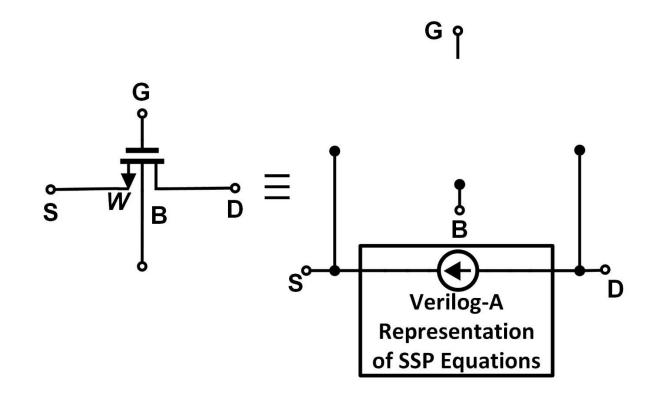

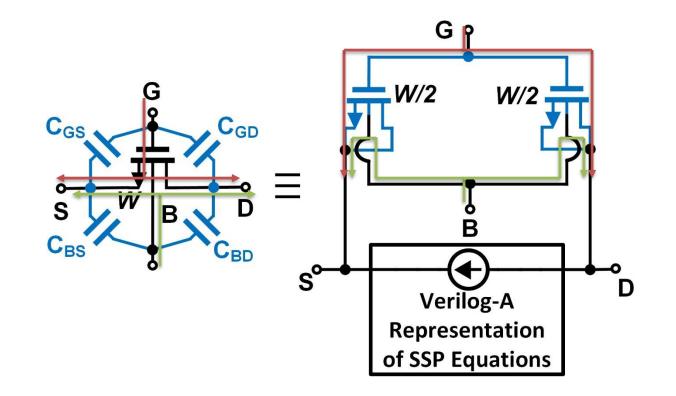

## **Simplified Surface Potential Model**

Simple Verilog-A code is employed to define the I<sub>DS</sub> based on FET terminal voltages using simplified surface potential (SSP) equations.

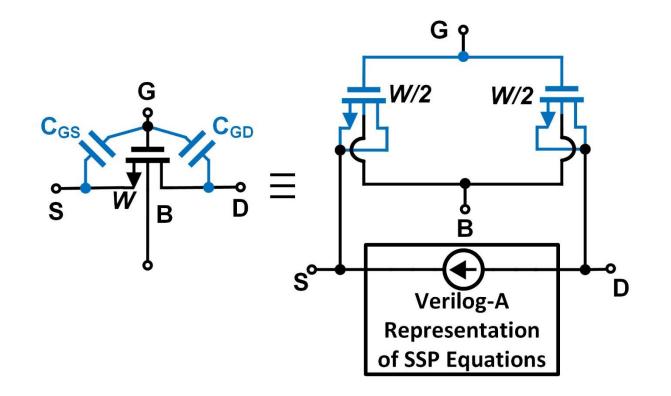

## **Simplified Surface Potential Model**

- Foundry provided model is used to take into account the 2<sup>nd</sup> order parasitics

- Gate-source and gate-drain capacitance.

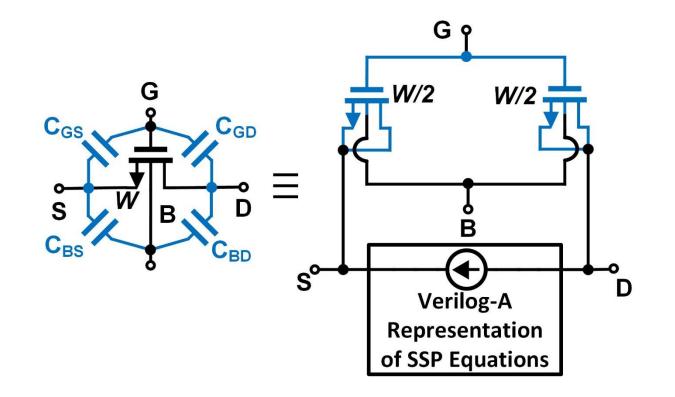

## **Simplified Surface Potential Model**

- Foundry provided model is used to take into account the 2<sup>nd</sup> order parasitics

- Body-source and body-drain capacitance.

## **Simplified Surface Potential Model**

- Foundry provided model is used to take into account the 2<sup>nd</sup> order parasitics

- Gate and body leakage currents.

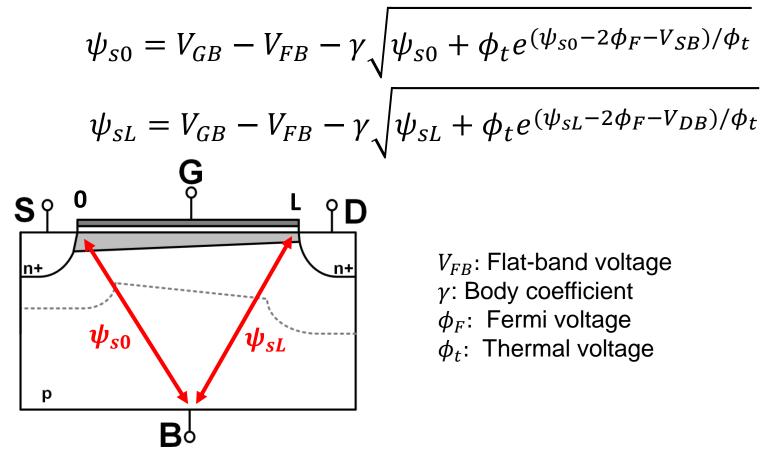

## **Surface Potential Equations**

• Surface potential at source and drain ends can be described by\*:

\* Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor. Oxford Univ. Press, 2011.

MO2B-2

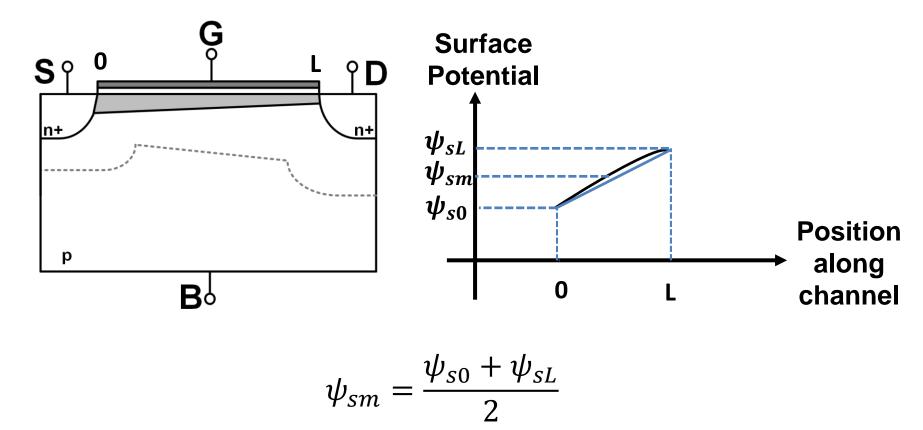

## **Surface Potential Along The Channel**

• Surface Potential along the channel can be approximated linearly.

## **Drain-Source Current Equation**

The drain-source current is a combination of drift and diffusion currents and can be approximated by\*:

$$\begin{split} I_{DS,total} &= I_{DS,drift} + I_{DS,diff}.\\ -I_{DS,drift} &= \frac{W}{L} \mu C_{ox} (V_{GB} - V_{FB} - \psi_{sm} - \gamma \sqrt{\psi_{sm}}) (\psi_{sL} - \psi_{s0}) \\ -I_{DS,diff.} &= \frac{W}{L} \mu C_{ox} \alpha_m \phi_t (\psi_{sL} - \psi_{s0}) \\ \alpha_m &= 1 + \frac{\gamma}{2\sqrt{\psi_{sm}}} \\ \psi_F &: \text{ Nobility of electron} \\ \psi_F &: \text{ Fermi voltage} \\ \gamma &: \text{ Body coefficient} \\ \phi_F &: \text{ Fermi voltage} \end{split}$$

#### Completely symmetric at $V_{DS}=0$ .

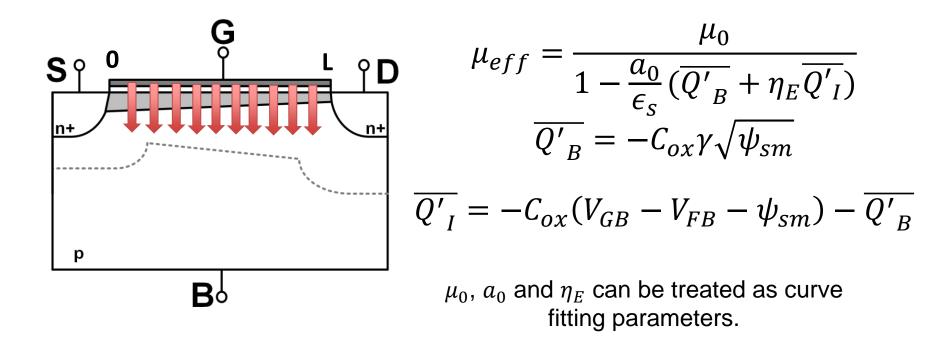

## **Effective Mobility**

• The mobility of electrons is reduced by the transverse field in the channel\*.

## Outline

- Motivation and Prior Art

- Simplified Surface Potential Model

- Short-Channel Effects

- Simulation and Measurement Results

- Conclusion

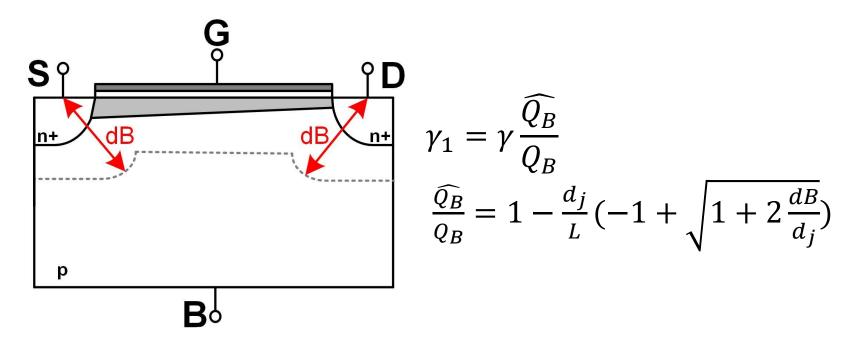

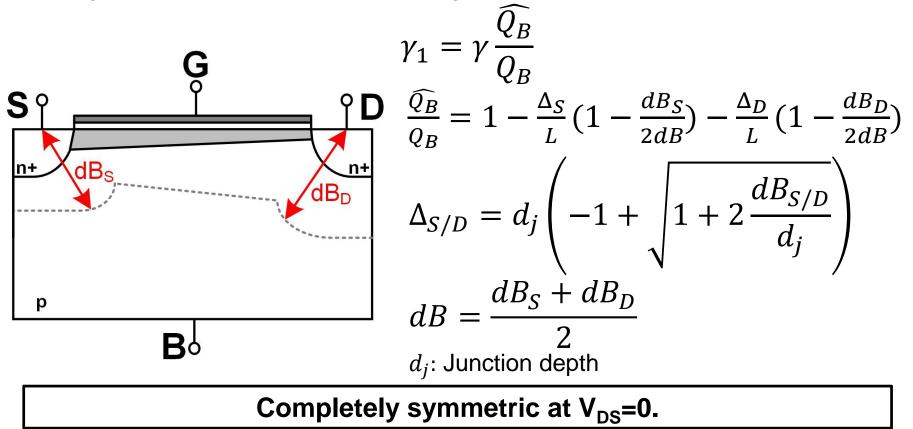

## **Charge Sharing**

• The extension of the drain and source depletion charge into the channel reduces the gate control over the channel charge.

Depletion region is not necessarily same around the source and drain.

## **Charge Sharing**

• The extension of the drain and source depletion charge into the channel reduces the gate control over the channel charge.

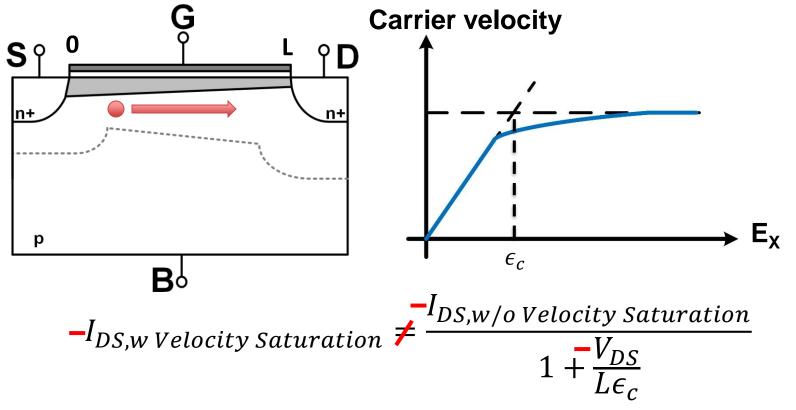

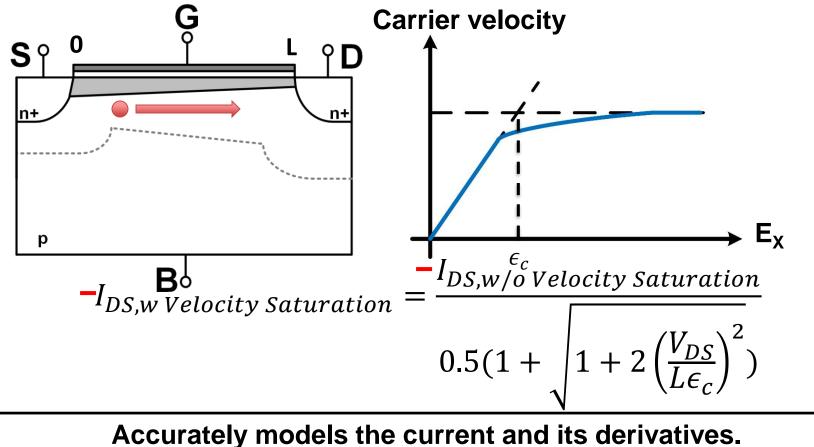

## **Velocity Saturation**

• Velocity of carriers can saturate even with device operating in triode.

#### Second order derivatives are discontinuous.

## **Velocity Saturation**

• Velocity of carriers can saturate even with device operating in triode.

• Channel length modulation can be described as:

$$L_{eff} = L - l_p$$

$$l_p = l_a \times \ln\left(1 + \frac{V_{DSX} - V_{DS,eff}}{V_e}\right), l_a = \sqrt{3t_{ox}d_j}$$

$t_{ox}$ : gate oxide thickness  $d_j$ : source and drain junction depth  $V_e$ : Early voltage

Smoothing functions are employed to ensure about the continuity of the current around V<sub>DS</sub>=0\*:

$$V_{DS,eff} = \frac{V_{DS}}{(1 + (\frac{V_{DS}}{V'_{DS}})^{10})^{0.1}}, V_{DSX} = \sqrt{V_{DS}^2 + 0.01 - 0.1}$$

$V'_{DS}$ : Smoothing function constant

\*X. Li et al., "PSP 102.3," NXP Semiconductors, Tech. Rep. 2008. MO2B-2

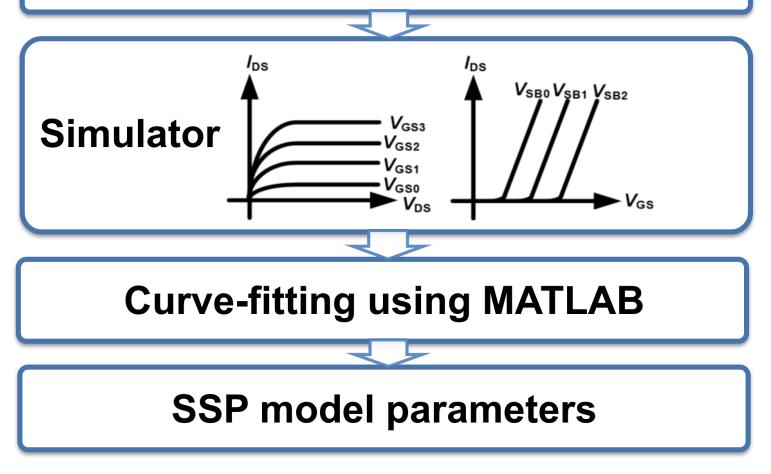

#### **Model Parameter Extraction**

#### Foundry provided model

## **PSP Model Versus SSP Model**

| <ul> <li>✓ Less than 20 parameters</li> <li>× Ignores temperature variation<br/>and process corners</li> <li>× Only used for transistors</li> <li>× Hundreds of parameters</li> <li>✓ Includes temperature<br/>variations and process corners</li> <li>✓ All regions of operation</li> </ul> | SSP Model                                                                                                        | PSP                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| operating as a switch                                                                                                                                                                                                                                                                        | <ul> <li>× Ignores temperature variation<br/>and process corners</li> <li>× Only used for transistors</li> </ul> | <ul> <li>✓ Includes temperature</li> <li>variations and process corners</li> </ul> |

#### **PSP Model Versus SSP Model**

# Only transistors operating as a switch are replaced with the SSP model.

## Outline

- Motivation and Prior Art

- Simplified Surface Potential Model

- Short-Channel Effects

- Simulation and Measurement Results

- Conclusion

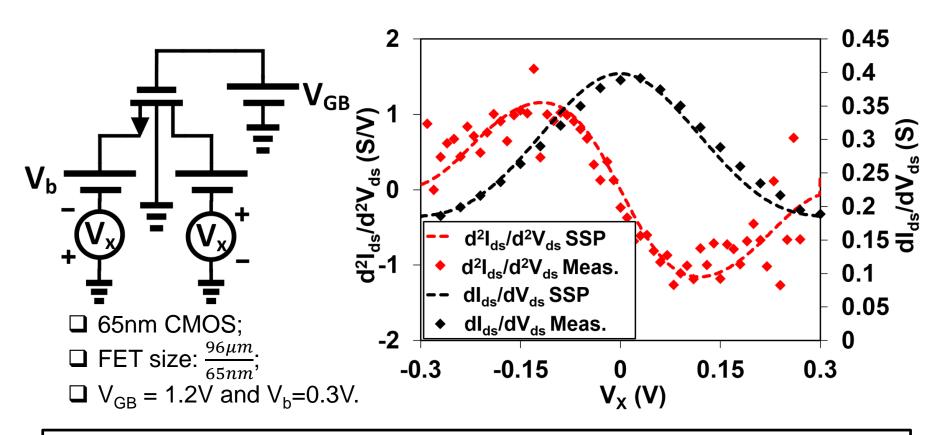

## **Measured Gummel Symmetry Test**

The SSP model accurately predicts  $I_{DS}$  and its derivatives.

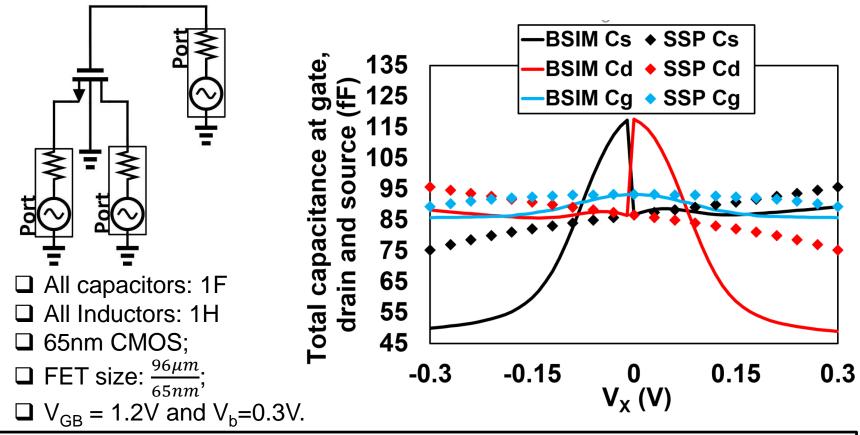

#### **Terminal Capacitance Simulation**

# The SSP model fixes the discontinuity in the terminal capacitances.

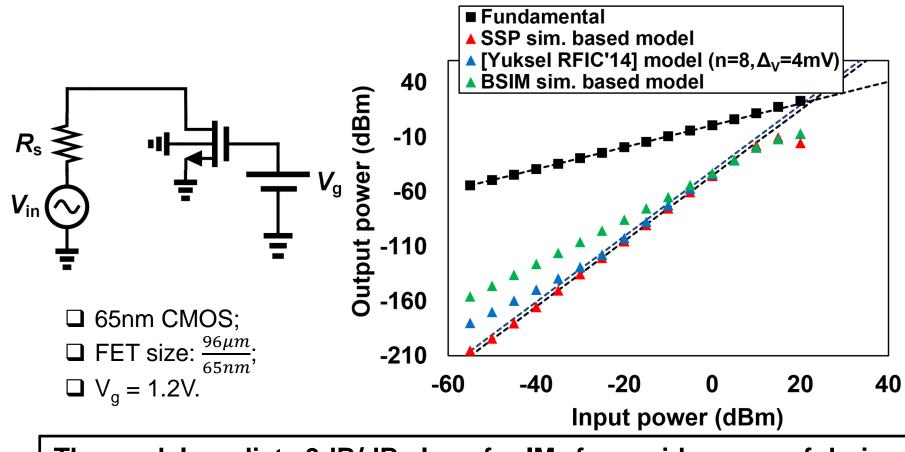

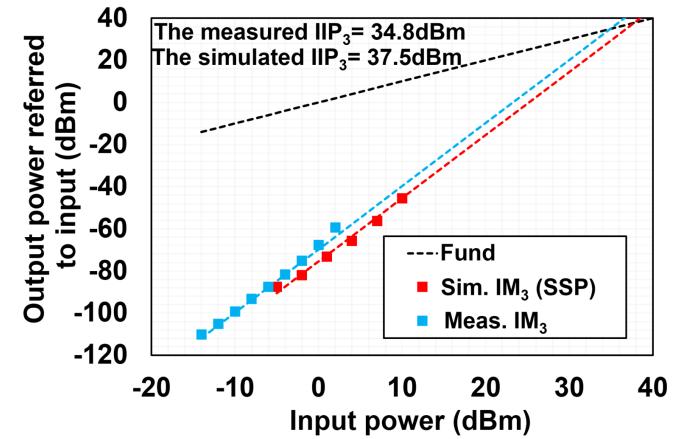

## FET IIP<sub>3</sub> Simulation

The model predicts 3dB/dB slope for IM<sub>3</sub> for a wide range of drainsource voltage across the FET.

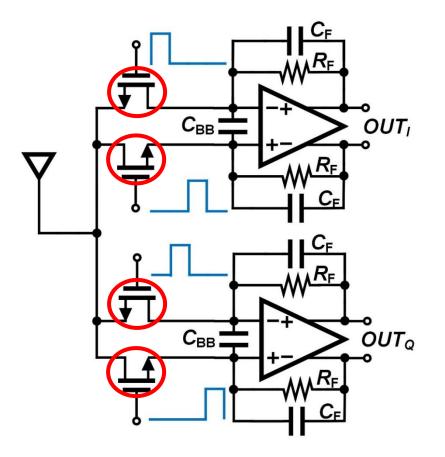

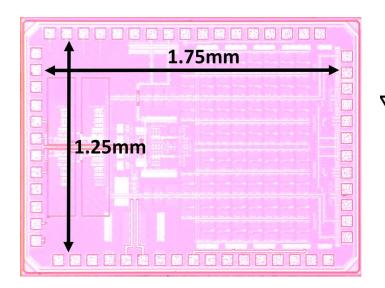

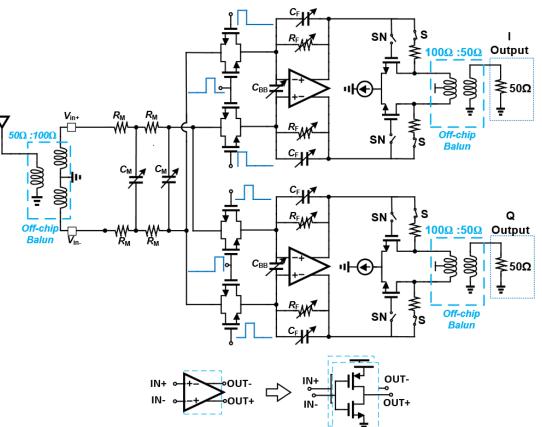

## 65nm CMOS Mixer-First Receiver

4-Path 0.15-2.5GHz passive-mixer-first receiver in 65nm CMOS.

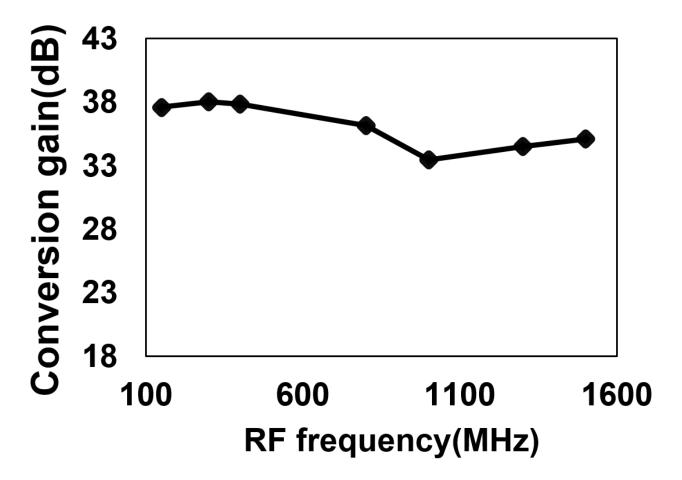

#### **Mixer-First Receiver Gain**

## **Mixer-First Receiver Out-of-Band IIP<sub>3</sub>**

The LO frequency is 300MHz and input tones are applied at 500MHz and 699MHz.

The SSP model predicts IIP<sub>3</sub> with better than 3dB precision.

## **Comparison Table**

|                                                                     | This work        | [Yuksel 14]       |

|---------------------------------------------------------------------|------------------|-------------------|

| Mixer-first receiver<br>OOB-IIP <sub>3</sub> simulation<br>accuracy | 3dB<br>(4-phase) | 4dB*<br>(8-phase) |

| Single switch<br>simulation time(s)**                               | 0.298            | 1.2               |

| Mixer first receiver simulation time(min)                           | 56***            | Not feasible      |

\*This is an 8-phase mixer-first receiver reported in [Andrews JSSC'10]. \*\*The computer is equipped with quad-core i7 CPU and 32GB physical memory, and simulations are performed on schematic level. \*\*\*Simulation is performed with the PSS-shooting method with number of harmonics equal to 175, the LO frequency is 300MHz and tones are applied at 500MHz and 680MHz and simulation is done for 3 power level point.

## Outline

- Motivation and Prior Art

- Simplified Surface Potential Model

- Short-Channel Effects

- Simulation and Measurement Results

- Conclusion

## Conclusion

- Digitally-driven foundries typically provide BSIM4 models that yield unphysical results when simulating passive mixer-like circuits.

- A simplified surface potential model is introduced that does not require measurements for model fitting, and leverages the foundry-provided models for capturing second-order parasitics.

- The SSP model is more computationally relaxed than prior art, and shows greater accuracy in simulating linearity of passive-mixer-like circuits.

- The model is available at <u>cosmic.ee.columbia.edu</u> for download.