Sub-mmWave Circuits and Systems in CMOS

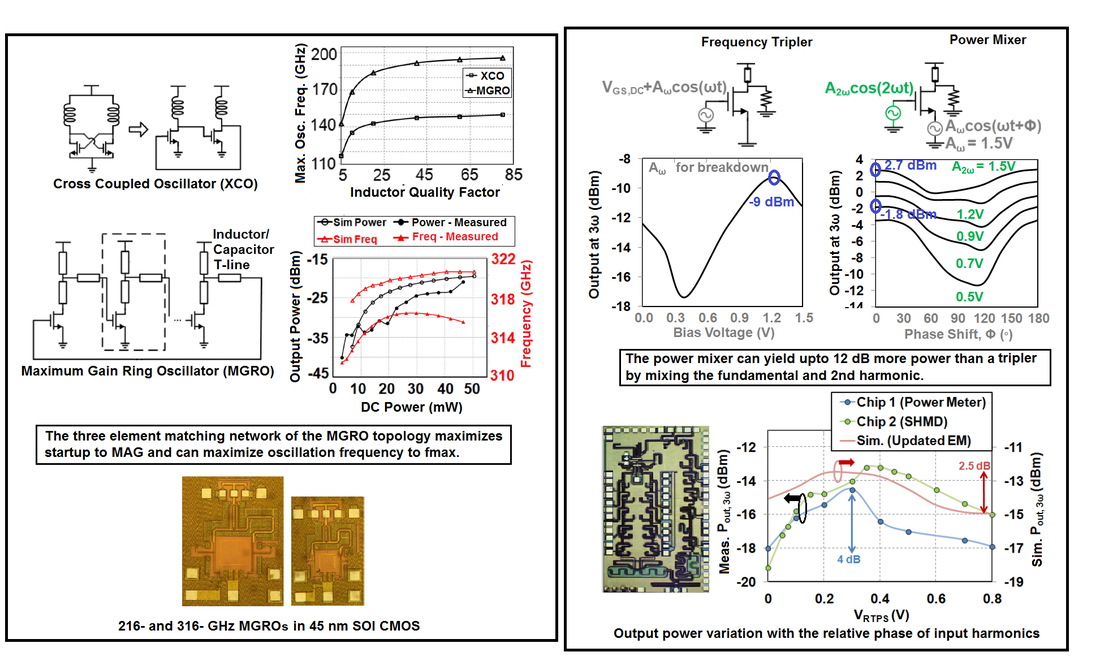

The terahertz frequency range, often defined as 300GHz-3THz and called the “terahertz gap”, has been historically unexplored as it lies beyond the cutoff frequencies of conventional electronics but is too low for the use of optical techniques. However, this frequency range remains interesting due to its potential applicability to medical imaging, security screening, bio-spectroscopy and high-data-rate short-range communication. The steady scaling of CMOS technology has provided us with CMOS transistors that have maximum oscillation frequencies (fmax) as high as 250-300GHz, making CMOS a potential platform for terahertz circuits and systems. However, new circuit design techniques must be developed to enable the operation of circuits near and beyond the technology fmax. We developed a new oscillator design methodology, dubbed the Maximum Gain Ring Oscillator (MGRO), which enables oscillators to function at the theoretically maximum oscillation frequency as dictated by the technology limits. In the proposed methodology, we embed matching networks within a ring oscillator so that each device is able to achieve its Maximum Available Gain (MAG). While MAG is purely a device metric that does not capture the loss in the passive components used for matching, we have developed design guidelines that maximize gain in the presence of passive component loss. Two MGROs were demonstrated that oscillate at ~110GHz and ~160GHz using the body-contacted devices in a 45nm SOI CMOS technology (fmax =200GHz). The second harmonic was extracted from these oscillators, resulting in signals at 220GHz and 320GHz with output power levels of -14dBm and -21dBm respectively [1],[2].

Based on device measurements carried out in our lab on CMOS technology nodes down to 45nm SOI, we predict that CMOS transistors will never exceed 300GHz in their fmax – while technology scaling is driving up the speed of the transistor channel, the wiring parasitics do not scale with technology and limit the speed of the device. Consequently, signal generation at terahertz frequencies in CMOS will always require the use of device nonlinearity for harmonic generation. Recently, we investigated and demonstrated the benefits of nonlinearity engineering in CMOS terahertz power mixers. We showed that in a single-FET mixer, the relative amplitudes and phases of the two input signals could be used to both engineer the nonlinearity of the device and apply greater input drive within device breakdown limits, greatly enhancing the output harmonic power. A power mixer that mixes a fundamental signal with its second harmonic can generate 16× higher output power at the third harmonic than a conventional tripler for appropriate input amplitudes and relative phase. A 200GHz power mixer in 130nm CMOS generates -13dBm of output power, which is 5× (7dB) higher than other 130nm sources at similar frequencies [3].

[1] Jahnavi Sharma and Harish Krishnaswamy, “215GHz CMOS signal source based on a Maximum-Gain Ring Oscillator topology,” in 2012 IEEE International Microwave Symposium Digest, pp.1-3, June 2012.

[2] Jahnavi Sharma and Harish Krishnaswamy, “216 and 316GHz 45nm SOI CMOS signal sources based on a Maximum-Gain Ring Oscillator topology,” IEEE Transactions on Microwave Theory and Techniques, vol. 61, no. 1, part 2, pp. 492-504, Jan. 2013.

[3] Jahnavi Sharma, Tolga Dinc and Harish Krishnaswamy, “A 200GHz Power Mixer in 130nm-CMOS Employing Nonlinearity Engineering,” in 2014 IEEE RFIC Symposium, June 2014.

Based on device measurements carried out in our lab on CMOS technology nodes down to 45nm SOI, we predict that CMOS transistors will never exceed 300GHz in their fmax – while technology scaling is driving up the speed of the transistor channel, the wiring parasitics do not scale with technology and limit the speed of the device. Consequently, signal generation at terahertz frequencies in CMOS will always require the use of device nonlinearity for harmonic generation. Recently, we investigated and demonstrated the benefits of nonlinearity engineering in CMOS terahertz power mixers. We showed that in a single-FET mixer, the relative amplitudes and phases of the two input signals could be used to both engineer the nonlinearity of the device and apply greater input drive within device breakdown limits, greatly enhancing the output harmonic power. A power mixer that mixes a fundamental signal with its second harmonic can generate 16× higher output power at the third harmonic than a conventional tripler for appropriate input amplitudes and relative phase. A 200GHz power mixer in 130nm CMOS generates -13dBm of output power, which is 5× (7dB) higher than other 130nm sources at similar frequencies [3].

[1] Jahnavi Sharma and Harish Krishnaswamy, “215GHz CMOS signal source based on a Maximum-Gain Ring Oscillator topology,” in 2012 IEEE International Microwave Symposium Digest, pp.1-3, June 2012.

[2] Jahnavi Sharma and Harish Krishnaswamy, “216 and 316GHz 45nm SOI CMOS signal sources based on a Maximum-Gain Ring Oscillator topology,” IEEE Transactions on Microwave Theory and Techniques, vol. 61, no. 1, part 2, pp. 492-504, Jan. 2013.

[3] Jahnavi Sharma, Tolga Dinc and Harish Krishnaswamy, “A 200GHz Power Mixer in 130nm-CMOS Employing Nonlinearity Engineering,” in 2014 IEEE RFIC Symposium, June 2014.

Copyright © Harish Krishnaswamy. All Rights Reserved.