Efficient-yet-Linear High-Power mmWave CMOS Transmitters

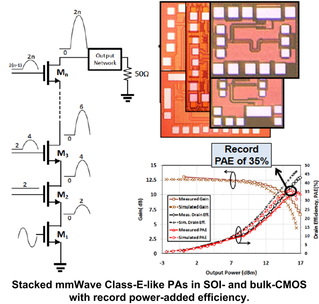

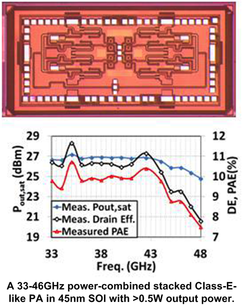

The most significant challenge facing CMOS mmWave systems is the limited output power of CMOS amplifiers. Operation at mmWave frequencies requires the use of scaled CMOS technologies that have extremely low breakdown voltages. This limits the output power that can be delivered to a load impedance. Conventional power enhancement techniques, such as impedance transformation and power combining, result in a drastic reduction in efficiency due to the low quality of CMOS passive components. Consequently, mmWave CMOS power amplifiers (PAs) have traditionally been limited in output power and efficiency to <15dBm and <20% respectively. CoSMIC lab has developed a design methodology for device stacking in mmWave CMOS PAs, a technique in which a series stack of devices is operated at a linearly larger supply voltage. The linearly larger output voltage swing is distributed among the various stacked devices so that each device still functions within its breakdown limits. CoSMIC lab has also demonstrated the feasibility of switch-mode power amplifiers at mmWave frequencies, and developed the design methodology for switch-mode stacked mmWave CMOS PAs. While switch-mode PAs are potentially more efficient than their linear PA counterparts, the series stacking of devices increases the effective switch resistance, reducing efficiency. We demonstrated a “Loss-Aware Class-E” design methodology that optimizes the load network tuning to maximize efficiency in stacked mmWave Class-E PAs [1]. We demonstrated stacked Class-E-like PAs in 45nm SOI CMOS at 45GHz that achieved output power levels of 17-20dBm at efficiencies as high as 35% (a world record for CMOS mmWave PAs) [2]-[4]. Combining these with large-scale, low-loss passive power combining techniques, we demonstrated a 45nm SOI CMOS power-combined PA array that achieved a peak saturated output power of >0.5W over a -1dB operation bandwidth of 33-46GHz (a world record in output power for CMOS mmWave PAs and 5× higher than the prior state of the art) [5]. This research was funded under the DARPA ELASTx program, and the latter result was extensively publicized by DARPA (link) [7].

A second fundamental challenge associated with power amplifiers is the trade-off between linearity, peak efficiency and back-off efficiency. Switching PA classes exhibit high peak efficiency but poor linearity. PAs also exhibit their peak efficiency at peak output power levels but show poor efficiency under back-off. We demonstrated a mmWave power DAC (digital-to-analog converter) architecture that simultaneously exploits large-scale power combining for high output power, switch-mode operation for high peak efficiency, supply switching for high efficiency under back-off and dynamic load modulation for linearity [5],[6]. A 3-bit direct digital-to-mmWave converter utilizing this architecture was fabricated and achieves 23.3dBm of saturated output power at 42.5GHz, a 6dB back-off PAE that is 68% of the peak PAE, and excellent linearity.

[1] Anandaroop Chakrabarti and Harish Krishnaswamy, “An Improved Analysis and Design Methodology for RF Class-E Power Amplifiers with Finite DC-feed Inductance and Switch On-Resistance,” in 2012 IEEE ISCAS, pp. 1763-1766, June 2012.

[2] Anandaroop Chakrabarti and Harish Krishnaswamy, “High Power, High Efficiency Stacked mmWave Class-E-like Power Amplifiers in 45nm SOI CMOS,” in Proc. 2012 IEEE Custom Integrated Circuits Conference, pp. 1-4, Sep. 2012.

[3] Anandaroop Chakrabarti and Harish Krishnaswamy, “High-Power, High-Efficiency, Class-E-like, Stacked mmWave PAs in SOI and bulk CMOS: Theory and Implementation,” accepted and to appear in IEEE Transactions on Microwave Theory and Techniques (available online).

[4] Anandaroop Chakrabarti, Jahnavi Sharma and Harish Krishnaswamy, “Dual-Output Stacked Class-EE Power Amplifiers in 45nm SOI CMOS for Q-band Applications,” in 2012 IEEE Compound Semiconductor IC Symposium, pp. 1-4, Oct. 2012.

[5] Ritesh Bhat, Anandaroop Chakrabarti and Harish Krishnaswamy, “Large-Scale Power-Combining and Linearization in Watt-Class mmWave CMOS Power Amplifiers,” in 2013 IEEE RFIC Symposium, pp. 283-286, June 2013.

[6] Anandaroop Chakrabarti and Harish Krishnaswamy, “Design Considerations for Stacked Class-E-like mmWave High-Speed Power DACs in CMOS,” in 2013 IEEE International Microwave Symposium Digest, pp. 1-4, June 2013.

[7] Iskren Abdomerovic, William D. Palmer, Paul M. Watson, Rick Worley, and Sanjay Raman, “Leveraging Integration: Toward Efficient Linearized All-Silicon IC Transmitters,” IEEE Microwave Magazine, vol. 15, no. 3, pp. 86-96, May 2014.

A second fundamental challenge associated with power amplifiers is the trade-off between linearity, peak efficiency and back-off efficiency. Switching PA classes exhibit high peak efficiency but poor linearity. PAs also exhibit their peak efficiency at peak output power levels but show poor efficiency under back-off. We demonstrated a mmWave power DAC (digital-to-analog converter) architecture that simultaneously exploits large-scale power combining for high output power, switch-mode operation for high peak efficiency, supply switching for high efficiency under back-off and dynamic load modulation for linearity [5],[6]. A 3-bit direct digital-to-mmWave converter utilizing this architecture was fabricated and achieves 23.3dBm of saturated output power at 42.5GHz, a 6dB back-off PAE that is 68% of the peak PAE, and excellent linearity.

[1] Anandaroop Chakrabarti and Harish Krishnaswamy, “An Improved Analysis and Design Methodology for RF Class-E Power Amplifiers with Finite DC-feed Inductance and Switch On-Resistance,” in 2012 IEEE ISCAS, pp. 1763-1766, June 2012.

[2] Anandaroop Chakrabarti and Harish Krishnaswamy, “High Power, High Efficiency Stacked mmWave Class-E-like Power Amplifiers in 45nm SOI CMOS,” in Proc. 2012 IEEE Custom Integrated Circuits Conference, pp. 1-4, Sep. 2012.

[3] Anandaroop Chakrabarti and Harish Krishnaswamy, “High-Power, High-Efficiency, Class-E-like, Stacked mmWave PAs in SOI and bulk CMOS: Theory and Implementation,” accepted and to appear in IEEE Transactions on Microwave Theory and Techniques (available online).

[4] Anandaroop Chakrabarti, Jahnavi Sharma and Harish Krishnaswamy, “Dual-Output Stacked Class-EE Power Amplifiers in 45nm SOI CMOS for Q-band Applications,” in 2012 IEEE Compound Semiconductor IC Symposium, pp. 1-4, Oct. 2012.

[5] Ritesh Bhat, Anandaroop Chakrabarti and Harish Krishnaswamy, “Large-Scale Power-Combining and Linearization in Watt-Class mmWave CMOS Power Amplifiers,” in 2013 IEEE RFIC Symposium, pp. 283-286, June 2013.

[6] Anandaroop Chakrabarti and Harish Krishnaswamy, “Design Considerations for Stacked Class-E-like mmWave High-Speed Power DACs in CMOS,” in 2013 IEEE International Microwave Symposium Digest, pp. 1-4, June 2013.

[7] Iskren Abdomerovic, William D. Palmer, Paul M. Watson, Rick Worley, and Sanjay Raman, “Leveraging Integration: Toward Efficient Linearized All-Silicon IC Transmitters,” IEEE Microwave Magazine, vol. 15, no. 3, pp. 86-96, May 2014.

Copyright © Harish Krishnaswamy. All Rights Reserved.